参数资料

| 型号: | AD9740ARUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/32页 |

| 文件大小: | 0K |

| 描述: | IC DAC 10BIT 210MSPS 28-TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 50 |

| 系列: | TxDAC® |

| 设置时间: | 11ns |

| 位数: | 10 |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 145mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 28-TSSOP |

| 包装: | 管件 |

| 输出数目和类型: | 2 电流,单极;2 电流,双极 |

| 采样率(每秒): | 210M |

| 产品目录页面: | 785 (CN2011-ZH PDF) |

| 配用: | AD9740ACP-PCBZ-ND - BOARD EVAL FOR AD9740ACP |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD9740

Rev. B | Page 15 of 32

transformer or differential amplifier. These common-mode

error sources include even-order distortion products and noise.

The enhancement in distortion performance becomes more

significant as the frequency content of the reconstructed

waveform increases and/or its amplitude decreases. This is due

to the first-order cancellation of various dynamic common-

mode distortion mechanisms, digital feedthrough, and noise.

Performing a differential-to-single-ended conversion via a

transformer also provides the ability to deliver twice the

reconstructed signal power to the load (assuming no source

termination). Because the output currents of IOUTA and

IOUTB are complementary, they become additive when

processed differentially. A properly selected transformer allows

the AD9740 to provide the required power and voltage levels to

different loads.

The output impedance of IOUTA and IOUTB is determined by

the equivalent parallel combination of the PMOS switches

associated with the current sources and is typically 100 kΩ in

parallel with 5 pF. It is also slightly dependent on the output

voltage (that is, VOUTA and VOUTB) due to the nature of a PMOS

device. As a result, maintaining IOUTA and/or IOUTB at a

virtual ground via an I-V op amp configuration results in the

optimum dc linearity. Note that the INL/DNL specifications for

the AD9740 are measured with IOUTA maintained at a virtual

ground via an op amp.

IOUTA and IOUTB also have a negative and positive voltage

compliance range that must be adhered to in order to achieve

optimum performance. The negative output compliance range

of 1 V is set by the breakdown limits of the CMOS process.

Operation beyond this maximum limit can result in a

breakdown of the output stage and affect the reliability of the

AD9740.

The positive output compliance range is slightly dependent on

the full-scale output current, IOUTFS. It degrades slightly from its

nominal 1.2 V for an IOUTFS = 20 mA to 1 V for an IOUTFS = 2 mA.

The optimum distortion performance for a single-ended or

differential output is achieved when the maximum full-scale

signal at IOUTA and IOUTB does not exceed 0.5 V.

DIGITAL INPUTS

The AD9740 digital section consists of 10 input bit channels

and a clock input. The 10-bit parallel data inputs follow

standard positive binary coding, where DB9 is the most

significant bit (MSB) and DB0 is the least significant bit (LSB).

IOUTA produces a full-scale output current when all data bits

are at Logic 1. IOUTB produces a complementary output with

the full-scale current split between the two outputs as a

function of the input code.

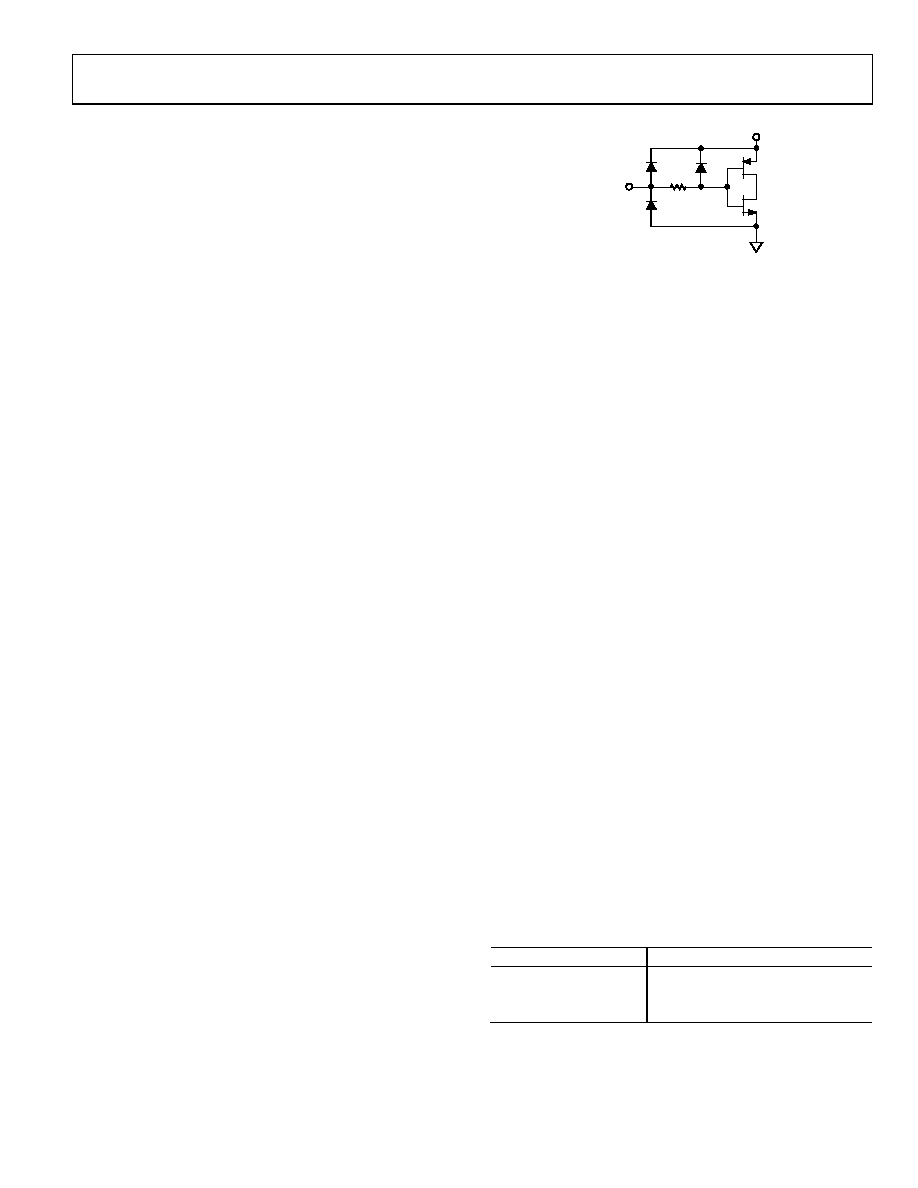

DVDD

DIGITAL

INPUT

02911-

024

Figure 26. Equivalent Digital Input

The digital interface is implemented using an edge-triggered

master/slave latch. The DAC output updates on the rising edge

of the clock and is designed to support a clock rate as high as

210 MSPS. The clock can be operated at any duty cycle that

meets the specified latch pulse width. The setup and hold times

can also be varied within the clock cycle as long as the specified

minimum times are met, although the location of these transition

edges can affect digital feedthrough and distortion performance.

Best performance is typically achieved when the input data

transitions on the falling edge of a 50% duty cycle clock.

CLOCK INPUT

SOIC/TSSOP Packages

The 28-lead package options have a single-ended clock input

(CLOCK) that must be driven to rail-to-rail CMOS levels. The

quality of the DAC output is directly related to the clock quality,

and jitter is a key concern. Any noise or jitter in the clock

translates directly into the DAC output. Optimal performance is

achieved if the CLOCK input has a sharp rising edge, because

the DAC latches are positive edge triggered.

LFCSP Package

A configurable clock input is available in the LFCSP package,

which allows for one single-ended and two differential modes.

The mode selection is controlled by the CMODE input, as

summarized in Table 6. Connecting CMODE to CLKCOM

selects the single-ended clock input. In this mode, the CLK+

input is driven with rail-to-rail swings and the CLK input is

left floating. If CMODE is connected to CLKVDD, then the

differential receiver mode is selected. In this mode, both inputs

are high impedance. The final mode is selected by floating

CMODE. This mode is also differential, but internal

terminations for positive emitter-coupled logic (PECL) are

activated. There is no significant performance difference

between any of the three clock input modes.

Table 6. Clock Mode Selection

CMODE Pin

Clock Input Mode

CLKCOM

Single-ended

CLKVDD

Differential

Float

PECL

The single-ended input mode operates in the same way as the

clock input in the 28-lead packages, as described previously.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9740ACPZ | IC DAC 10BIT 210MSPS 32-LFCSP |

| VI-J4R-MZ-F4 | CONVERTER MOD DC/DC 7.5V 25W |

| VI-J4R-MZ-F3 | CONVERTER MOD DC/DC 7.5V 25W |

| VI-J4L-MZ-F1 | CONVERTER MOD DC/DC 28V 25W |

| AD5308BRUZ | IC DAC 8BIT OCTAL W/BUFF 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9740ARUZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 210 MSPS TxDAC D/A Converter |

| AD9740ARUZRL7 | 功能描述:IC DAC 10BIT 210MSPS 28-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 产品培训模块:LTC263x 12-, 10-, and 8-Bit VOUT DAC Family 特色产品:LTC2636 - Octal 12-/10-/8-Bit SPI VOUT DACs with 10ppm/°C Reference 标准包装:91 系列:- 设置时间:4µs 位数:10 数据接口:MICROWIRE?,串行,SPI? 转换器数目:8 电压电源:单电源 功率耗散(最大):2.7mW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-DFN-EP(4x3) 包装:管件 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD9740ARZ | 功能描述:IC DAC 10BIT 210MSPS 28-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

| AD9740ARZRL | 功能描述:IC DAC 10BIT 210MSPS 28-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 产品培训模块:LTC263x 12-, 10-, and 8-Bit VOUT DAC Family 特色产品:LTC2636 - Octal 12-/10-/8-Bit SPI VOUT DACs with 10ppm/°C Reference 标准包装:91 系列:- 设置时间:4µs 位数:10 数据接口:MICROWIRE?,串行,SPI? 转换器数目:8 电压电源:单电源 功率耗散(最大):2.7mW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-DFN-EP(4x3) 包装:管件 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD9740-EB | 制造商:Analog Devices 功能描述:10 BIT 100 MSPS CMOS DAC - Bulk |

发布紧急采购,3分钟左右您将得到回复。