- 您现在的位置:买卖IC网 > PDF目录17065 > AD9750-EB (Analog Devices Inc)BOARD EVAL FOR AD9750 PDF资料下载

参数资料

| 型号: | AD9750-EB |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/22页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9750 |

| 产品培训模块: | DAC Architectures |

| 标准包装: | 1 |

| 系列: | TxDAC® |

| DAC 的数量: | 1 |

| 位数: | 10 |

| 采样率(每秒): | 125M |

| 数据接口: | 并联 |

| 设置时间: | 35ns |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD9750 |

| 相关产品: | AD9750ARZ-ND - IC DAC 10BIT 125MSPS 28-SOIC AD9750ARUZ-ND - IC DAC 10BIT 125MSPS 28TSSOP AD9750ARUZRL7-ND - IC DAC 10BIT 125MSPS 28TSSOP AD9750ARZRL-ND - IC DAC 10BIT 125MSPS 28SOIC |

AD9750

–10–

REV. 0

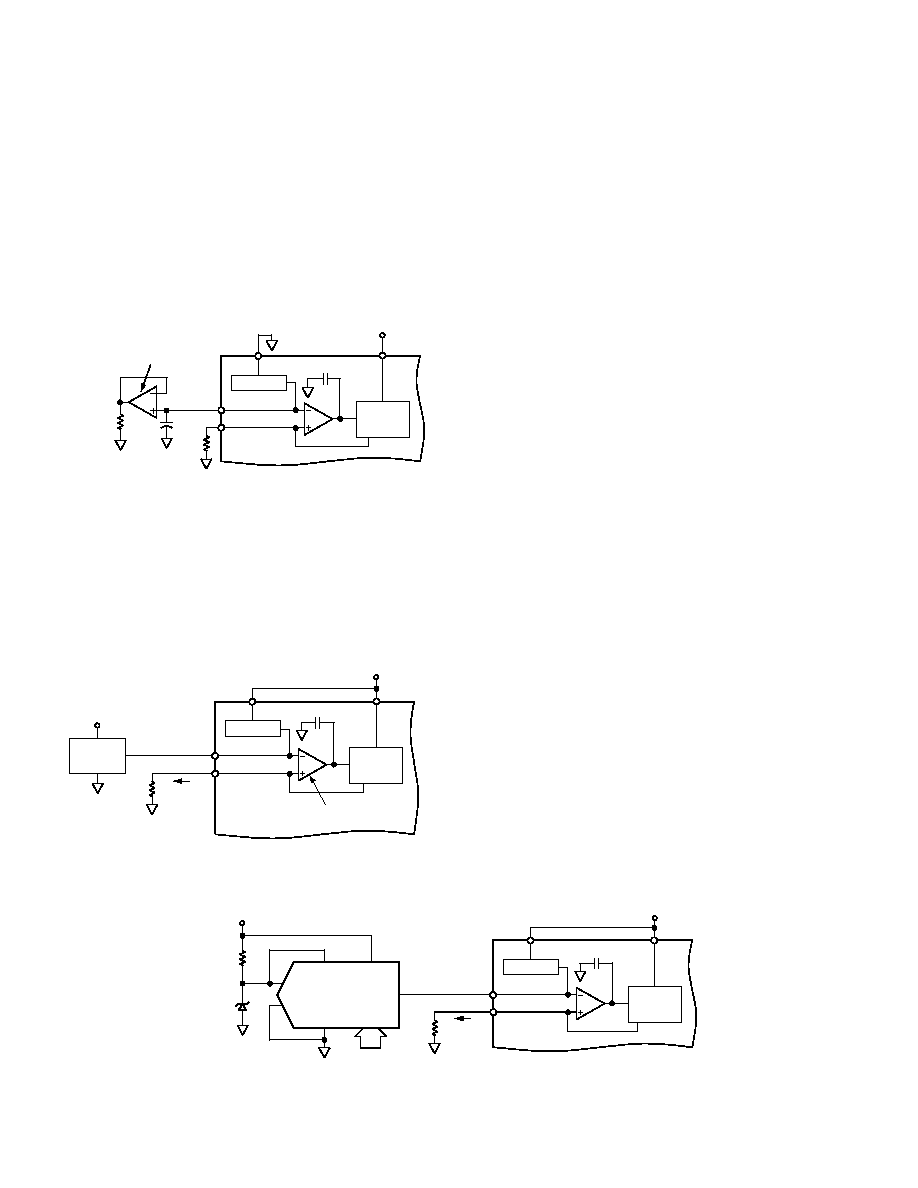

REFERENCE OPERATION

The AD9750 contains an internal 1.20 V bandgap reference

that can easily be disabled and overridden by an external refer-

ence. REFIO serves as either an input or output depending on

whether the internal or an external reference is selected. If

REFLO is tied to ACOM, as shown in Figure 18, the internal

reference is activated and REFIO provides a 1.20 V output. In

this case, the internal reference must be compensated externally

with a ceramic chip capacitor of 0.1

F or greater from REFIO

to REFLO. Also, REFIO should be buffered with an external

amplifier having an input bias current less than 100 nA if any

additional loading is required.

150pF

+1.2V REF

AVDD

REFLO

CURRENT

SOURCE

ARRAY

+5V

REFIO

FS ADJ

2k

0.1 F

AD9750

ADDITIONAL

LOAD

OPTIONAL

EXTERNAL

REF BUFFER

Figure 18. Internal Reference Configuration

The internal reference can be disabled by connecting REFLO to

AVDD. In this case, an external reference may then be applied

to REFIO as shown in Figure 19. The external reference may

provide either a fixed reference voltage to enhance accuracy and

drift performance or a varying reference voltage for gain control.

Note that the 0.1

F compensation capacitor is not required

since the internal reference is disabled, and the high input im-

pedance (i.e., 1 M

) of REFIO minimizes any loading of the

external reference.

150pF

+1.2V REF

AVDD

REFLO

CURRENT

SOURCE

ARRAY

AVDD

REFIO

FS ADJ

RSET

AD9750

EXTERNAL

REF

IREF =

VREFIO/RSET

AVDD

REFERENCE

CONTROL

AMPLIFIER

VREFIO

Figure 19. External Reference Configuration

REFERENCE CONTROL AMPLIFIER

The AD9750 also contains an internal control amplifier that is

used to regulate the DAC’s full-scale output current, IOUTFS.

The control amplifier is configured as a V-I converter as shown

in Figure 19, such that its current output, IREF, is determined by

the ratio of the VREFIO and an external resistor, RSET, as stated

in Equation 4. IREF is copied over to the segmented current

sources with the proper scaling factor to set IOUTFS as stated in

Equation 3.

The control amplifier allows a wide (10:1) adjustment span of

IOUTFS over a 2 mA to 20 mA range by setting IREF between

62.5

A and 625 A. The wide adjustment span of I

OUTFS

provides several application benefits. The first benefit relates

directly to the power dissipation of the AD9750, which is

proportional to IOUTFS (refer to the Power Dissipation section).

The second benefit relates to the 20 dB adjustment, which is

useful for system gain control purposes.

The small signal bandwidth of the reference control amplifier is

approximately 0.5 MHz. The output of the control amplifier is

internally compensated via a 150 pF capacitor that limits the

control amplifier small-signal bandwidth and reduces its

output impedance. Since the –3 dB bandwidth corresponds to

the dominant pole, and hence the time constant, the settling

time of the control amplifier to a stepped reference input re-

sponse can be approximated. In this case, the time constant can

be approximated to be 320 ns.

There are two methods in which IREF can be varied for a fixed

RSET. The first method is suitable for a single-supply system in

which the internal reference is disabled, and the common-mode

voltage of REFIO is varied over its compliance range of 1.25 V

to 0.10 V. REFIO can be driven by a single-supply amplifier or

DAC, thus allowing IREF to be varied for a fixed RSET. Since the

input impedance of REFIO is approximately 1 M

, a simple,

low cost R-2R ladder DAC configured in the voltage mode

topology may be used to control the gain. This circuit is shown

in Figure 20 using the AD7524 and an external 1.2 V reference,

the AD1580.

The second method may be used in a dual-supply system in

which the common-mode voltage of REFIO is fixed and IREF is

varied by an external voltage, VGC, applied to RSET via an ampli-

fier. An example of this method is shown in Figure 21, in which

the internal reference is used to set the common-mode voltage

of the control amplifier to 1.20 V. The external voltage, VGC, is

referenced to ACOM and should not exceed 1.2 V. The value of

RSET is such that IREFMAX and IREFMIN do not exceed 62.5 A

1.2V

150pF

+1.2V REF

AVDD

REFLO

CURRENT

SOURCE

ARRAY

AVDD

REFIO

FS ADJ

RSET

AD9750

IREF =

VREF/RSET

AVDD

VREF

VDD

RFB

OUT1

OUT2

AGND

DB7–DB0

AD7524

AD1580

0.1V TO 1.2V

Figure 20. Single-Supply Gain Control Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| UPS2E471MRD | CAP ALUM 470UF 250V 20% RADIAL |

| EVAL-AD5532HSEBZ | BOARD EVAL FOR AD5532HS |

| DC939A | BOARD DELTA SIGMA ADC LTC2484 |

| LGU2W680MELY | CAP ALUM 68UF 450V 20% SNAP |

| EVAL-AD5516-1EBZ | BOARD EVAL FOR AD5516-1 2.5V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9750-EBZ | 功能描述:BOARD EVAL FOR AD9750 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:TxDAC® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| AD9751 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 300 MSPS High-Speed TxDAC+ D/A Converter |

| AD9751AST | 制造商:Analog Devices 功能描述:DAC 1-CH Segment 10-bit 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:10-BIT, 300 MSPS TXDAC+ D/A CONVERTER - Bulk 制造商:Analog Devices 功能描述:IC 10-BIT DAC |

| AD9751ASTRL | 制造商:Analog Devices 功能描述:DAC 1-CH Segment 10-bit 48-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:10-BIT, 300 MSPS TXDAC+ D/A CONVERTER - Tape and Reel |

| AD9751ASTZ | 功能描述:IC DAC 10BIT 300MSPS 48-LQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC+® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 设置时间:4µs 位数:12 数据接口:串行 转换器数目:2 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-uMAX 包装:管件 输出数目和类型:2 电压,单极 采样率(每秒):* 产品目录页面:1398 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。