- 您现在的位置:买卖IC网 > PDF目录17063 > AD9760-EBZ (Analog Devices Inc)BOARD EVAL FOR AD9760 PDF资料下载

参数资料

| 型号: | AD9760-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/23页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9760 |

| 产品培训模块: | DAC Architectures |

| 标准包装: | 1 |

| 系列: | TxDAC® |

| DAC 的数量: | 1 |

| 位数: | 10 |

| 采样率(每秒): | 125M |

| 数据接口: | 并联 |

| 设置时间: | 35ns |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD9760 |

| 相关产品: | AD9760ARZ-ND - IC DAC 10BIT 125MSPS 28-SOIC AD9760ARZ50-ND - IC DAC 10BIT 50MSPS 28-SOIC AD9760ARZRL-ND - IC DAC 10BIT 125MSPS 28-SOIC AD9760ARUZRL7-ND - IC DAC 10BIT 125MSPS 28TSSOP AD9760ARUZ-ND - IC DAC 10BIT 125MSPS 28-TSSOP AD9760ARU50RL7-ND - IC DAC 10BIT 50MSPS 28-TSSOP AD9760ARU-ND - IC DAC 10BIT 125MSPS 28-TSSOP AD9760AR50-ND - IC DAC 10BIT 50MSPS 28-SOIC AD9760AR-ND - IC DAC 10BIT 125MSPS 28-SOIC AD9760ARU50-ND - IC DAC 10BIT 50MSPS 28-TSSOP |

AD9760

–11–

REV. B

FUNCTIONAL DESCRIPTION

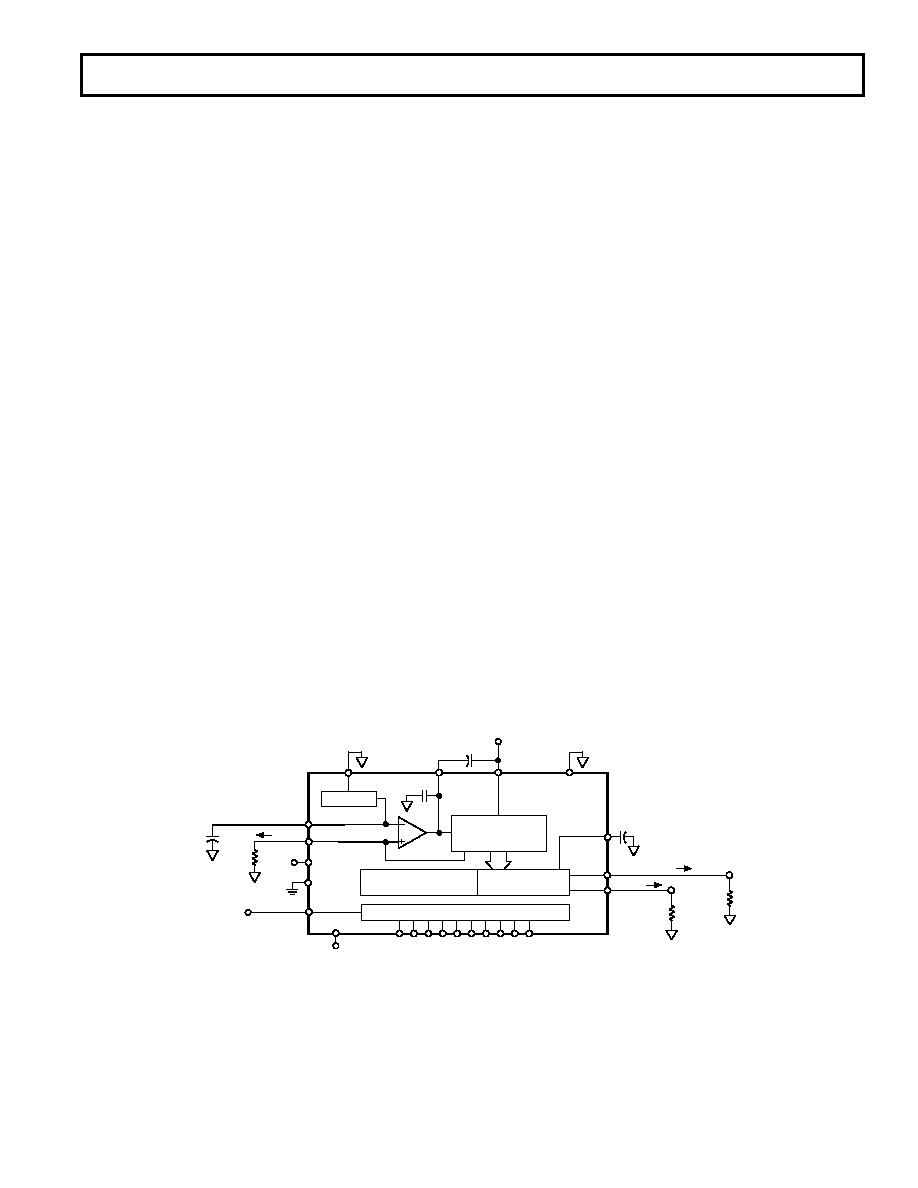

Figure 39 shows a simplified block diagram of the AD9760.

The AD9760 consists of a large PMOS current source array that

is capable of providing up to 20 mA of total current. The array

is divided into 31 equal currents that make up the 5 most sig-

nificant bits (MSBs). The next 4 bits or middle bits consist

of 15 equal current sources whose value is 1/16th of an MSB

current source. The remaining LSBs is a binary weighted frac-

tion of the middle-bits current sources. Implementing the

middle and lower bits with current sources, instead of an R-2R

ladder, enhances its dynamic performance for multitone or low

amplitude signals and helps maintain the DAC’s high output

impedance (i.e., >100 k

).

All of these current sources are switched to one or the other of

the two output nodes (i.e., IOUTA or IOUTB) via PMOS differen-

tial current switches. The switches are based on a new architec-

ture that drastically improves distortion performance. This new

switch architecture reduces various timing errors and provides

matching complementary drive signals to the inputs of the dif-

ferential current switches.

The analog and digital sections of the AD9760 have separate

power supply inputs (i.e., AVDD and DVDD) that can operate

independently over a 2.7 volt to 5.5 volt range. The digital

section, which is capable of operating up to a 125 MSPS clock

rate, consists of edge-triggered latches and segment decoding

logic circuitry. The analog section includes the PMOS current

sources, the associated differential switches, a 1.20 V bandgap

voltage reference and a reference control amplifier.

The full-scale output current is regulated by the reference con-

trol amplifier and can be set from 2 mA to 20 mA via an exter-

nal resistor, RSET. The external resistor, in combination with

both the reference control amplifier and voltage reference

VREFIO, sets the reference current IREF, which is mirrored over to

the segmented current sources with the proper scaling factor.

The full-scale current, IOUTFS, is thirty-two times the value of IREF.

DAC TRANSFER FUNCTION

The AD9760 provides complementary current outputs, IOUTA

and IOUTB. IOUTA will provide a near full-scale current output,

IOUTFS, when all bits are high (i.e., DAC CODE = 1023) while

IOUTB, the complementary output, provides no current. The

current output appearing at IOUTA and IOUTB is a function of

both the input code and IOUTFS and can be expressed as:

IOUTA = (DAC CODE/1024)

× IOUTFS

(1)

IOUTB = (1023 – DAC CODE)/1024

× IOUTFS

(2)

where DAC CODE = 0 to 1023 (i.e., Decimal Representation).

As mentioned previously, IOUTFS is a function of the reference

current IREF, which is nominally set by a reference voltage,

VREFIO and external resistor RSET. It can be expressed as:

IOUTFS = 32

× IREF

(3)

where IREF = VREFIO/RSET

(4)

The two current outputs will typically drive a resistive load

directly or via a transformer. If dc coupling is required, IOUTA

and IOUTB should be directly connected to matching resistive

loads, RLOAD, that are tied to analog common, ACOM. Note,

RLOAD may represent the equivalent load resistance seen by

IOUTA or IOUTB as would be the case in a doubly terminated

50

or 75 cable. The single-ended voltage output appearing

at the IOUTA and IOUTB nodes is simply:

VOUTA = IOUTA

× RLOAD

(5)

VOUTB = IOUTB

× RLOAD

(6)

Note the full-scale value of VOUTA and VOUTB should not exceed

the specified output compliance range to maintain specified

distortion and linearity performance.

DIGITAL DATA INPUTS (DB9–DB0)

50pF

COMP1

+1.20V REF

AVDD

ACOM

REFLO

COMP2

PMOS

CURRENT SOURCE

ARRAY

0.1 F

+5V

SEGMENTED SWITCHES

FOR DB9–DB1

LSB

SWITCH

REFIO

FS ADJ

DVDD

DCOM

CLOCK

+5V

RSET

2k

0.1 F

IOUTA

IOUTB

0.1 F

AD9760

SLEEP

LATCHES

IREF

VREFIO

CLOCK

IOUTB

IOUTA

RLOAD

50

VOUTB

VOUTA

RLOAD

50

VDIFF = VOUTA – VOUTB

Figure 39. Functional Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| AD9748ACP-PCBZ | BOARD EVAL FOR AD9748ACP |

| GCM18DCTD-S288 | CONN EDGECARD 36POS .156 EXTEND |

| GBM24DSEI-S243 | CONN EDGECARD 48POS .156 EYELET |

| GBM15DSEF-S243 | CONN EDGECARD 30POS .156 EYELET |

| GCM10DCST-S288 | CONN EDGECARD 20POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9761 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual 10-Bit TxDAC+⑩ with 2x Interpolation Filters |

| AD9761ARS | 功能描述:IC DAC 10BIT DUAL 40MSPS 28-SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD9761-ARS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:10-Bit Digital-to-Analog Converter |

| AD9761ARSRL | 功能描述:IC DAC 10BIT DUAL 40MSPS 28-SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD9761ARSZ | 功能描述:IC DAC 10BIT DUAL 40MSPS 28-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 设置时间:4µs 位数:12 数据接口:串行 转换器数目:2 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-uMAX 包装:管件 输出数目和类型:2 电压,单极 采样率(每秒):* 产品目录页面:1398 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。