- 您现在的位置:买卖IC网 > PDF目录10979 > AD9859YSVZ (Analog Devices Inc)IC DDS DAC 10BIT 400MSPS 48-TQFP PDF资料下载

参数资料

| 型号: | AD9859YSVZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/24页 |

| 文件大小: | 0K |

| 描述: | IC DDS DAC 10BIT 400MSPS 48-TQFP |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 标准包装: | 1 |

| 分辨率(位): | 10 b |

| 主 fclk: | 400MHz |

| 调节字宽(位): | 32 b |

| 电源电压: | 1.71 V ~ 1.96 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TQFP 裸露焊盘 |

| 供应商设备封装: | 48-TQFP 裸露焊盘(7x7) |

| 包装: | 托盘 |

| 产品目录页面: | 552 (CN2011-ZH PDF) |

AD9859

Rev. A | Page 11 of 24

THEORY OF OPERATION

COMPONENT BLOCKS

DDS Core

The output frequency (fO) of the DDS is a function of the

frequency of the system clock (SYSCLK), the value of the

frequency tuning word (FTW), and the capacity of the

accumulator (232 in this case). The exact relationship is given

below with fS defined as the frequency of SYSCLK.

31

32

2

0

2

/

FTW

with

f

FTW

f

S

O

1

–

2

/

–

1

32

31

32

FTW

with

FTW

f

S

O

The value at the output of the phase accumulator is translated to

an amplitude value via the COS(x) functional block and routed

to the DAC.

In certain applications, it is desirable to force the output signal

to zero phase. Simply setting the FTW to 0 does not accomplish

this; it only results in the DDS core holding its current phase

value. Thus, a control bit is required to force the phase accumula-

tor output to zero.

At power-up, the clear phase accumulator bit is set to Logic 1,

but the buffer memory for this bit is cleared (Logic 0). There-

fore, upon power-up, the phase accumulator remains clear until

the first I/O UPDATE is issued.

Phase-Locked Loop (PLL)

The PLL allows multiplication of the REFCLK frequency.

Control of the PLL is accomplished by programming the 5-bit

REFCLK multiplier portion of Control Function Register No. 2,

Bits <7:3>.

When programmed for values ranging from 0x04 to 0x14

(4 decimal to 20 decimal), the PLL multiplies the REFCLK

input frequency by the corresponding decimal value. However,

the maximum output frequency of the PLL is restricted to

400 MHz. Whenever the PLL value is changed, the user should

be aware that time must be allocated to allow the PLL to lock

(approximately 1 ms).

The PLL is bypassed by programming a value outside the range

of 4 to 20 (decimal). When bypassed, the PLL is shut down to

conserve power.

Clock Input

The AD9859 supports various clock methodologies. Support for

differential or single-ended input clocks and enabling of an

on-chip oscillator and/or a phase-locked loop (PLL) multiplier

are all controlled via user programmable bits. The AD9859 may

be configured in one of six operating modes to generate the system

clock. The modes are configured using the CLKMODESELECT

pin, CFR1<4>, and CFR2<7:3>. Connecting the external pin

CLKMODESELECT to Logic High enables the on-chip crystal

oscillator circuit. With the on-chip oscillator enabled, users of

the AD9859 connect an external crystal to the REFCLK and

REFCLKB inputs to produce a low frequency reference clock in

the range of 20 MHz to 30 MHz. The signal generated by the

oscillator is buffered before it is delivered to the rest of the chip.

This buffered signal is available via the CRYSTAL OUT pin. Bit

CFR1<4> can be used to enable or disable the buffer, turning on

or off the system clock. The oscillator itself is not powered

down in order to avoid long startup times associated with

turning on a crystal oscillator. Writing CFR2<9> to Logic High

enables the crystal oscillator output buffer. Logic Low at

CFR2<9> disables the oscillator output buffer.

Connecting CLKMODESELECT to Logic Low disables the

on-chip oscillator and the oscillator output buffer. With the

oscillator disabled, an external oscillator must provide the

REFCLK and/or REFCLKB signals. For differential operation,

these pins are driven with complementary signals. For single-

ended operation, a 0.1 μF capacitor should be connected

between the unused pin and the analog power supply. With the

capacitor in place, the clock input pin bias voltage is 1.35 V. In

addition, the PLL may be used to multiply the reference

frequency by an integer value in the range of 4 to 20. Table 4

summarizes the clock modes of operation. Note that the PLL

multiplier is controlled via the CFR2<7:3> bits, independent of

the CFR1<4> bit.

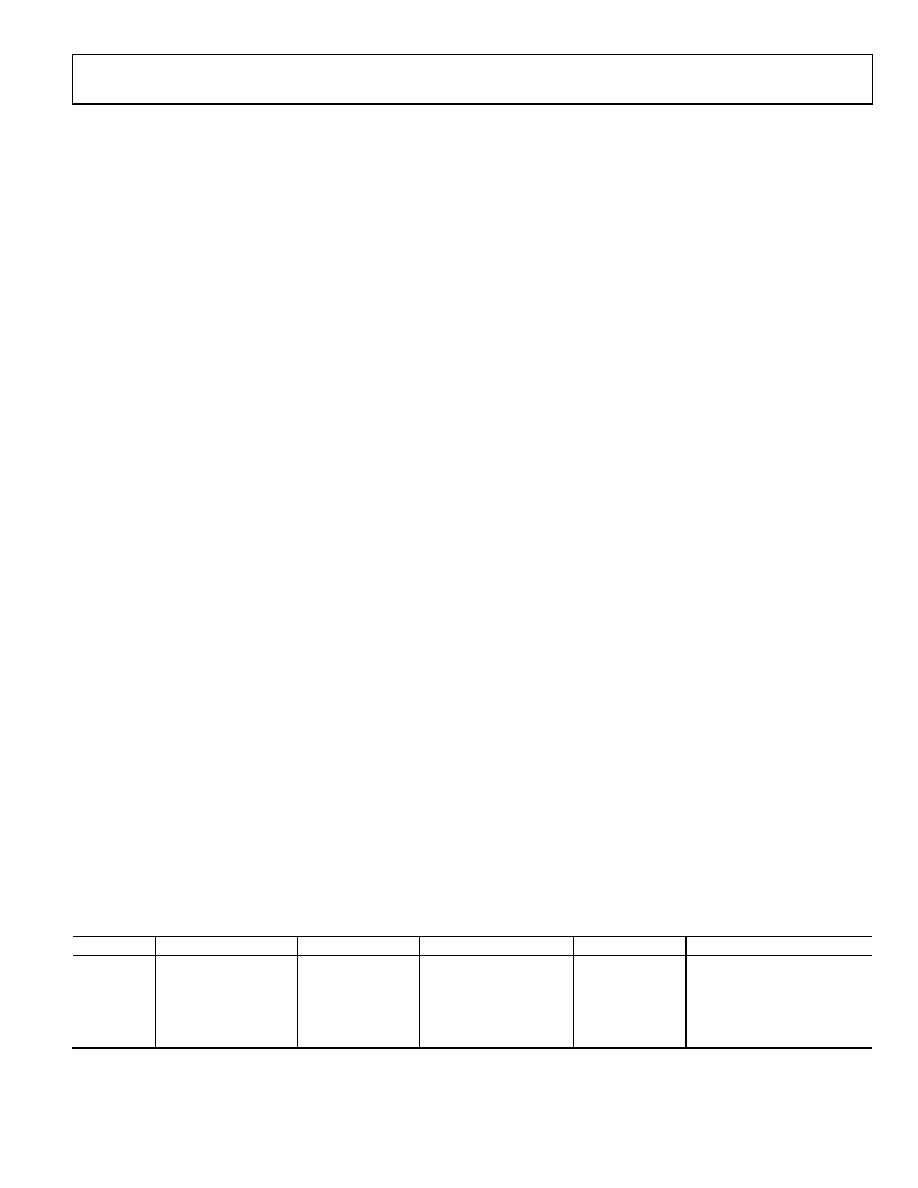

Table 4. Clock Input Modes of Operation

CFR1<4>

CLKMODESELECT

CFR2<7:3>

Oscillator Enabled?

System Clock

Frequency Range (MHz)

Low

High

3 < M < 21

Yes

FCLK = FOSC × M

80 < FCLK < 400

Low

High

M < 4 or M > 20

Yes

FCLK = FOSC

20 < FCLK < 30

Low

3 < M < 21

No

FCLK = FOSC × M

80 < FCLK < 400

Low

M < 4 or M > 20

No

FCLK = FOSC

10 < FCLK < 400

High

X

No

FCLK = 0

N/A

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B1K-IX-B1 | CONVERTER MOD DC/DC 40V 75W |

| AD9913BCPZ | IC DDS 10BIT DAC 250MSPS 32LFCSP |

| MCF51JE128CMB | IC MCU 128K COLDF 81-PBGA |

| AD5930YRUZ | IC GEN PROG FREQ BURST 20TSSOP |

| S9S12HY64J0MLL | MCU 64K FLASH AUTO 100-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9859YSVZ | 制造商:Analog Devices 功能描述:IC 400 MSPS DDS 制造商:Analog Devices 功能描述:IC, 400 MSPS DDS |

| AD9859YSVZ | 制造商:Analog Devices 功能描述:DIRECT DIGITAL SYNTHESIZER |

| AD9859YSVZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:400 MSPS, 10-Bit,1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSVZ-REEL7 | 功能描述:IC DDS DAC 10BIT 400MSPS 48TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9859YSVZ-REEL71 | 制造商:AD 制造商全称:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

发布紧急采购,3分钟左右您将得到回复。