- 您现在的位置:买卖IC网 > PDF目录378277 > ADC08100 (National Semiconductor Corporation) 8-Bit, 20 MSPS to 100 MSPS, 1.3 mW/MSPS A/D Converter PDF资料下载

参数资料

| 型号: | ADC08100 |

| 厂商: | National Semiconductor Corporation |

| 英文描述: | 8-Bit, 20 MSPS to 100 MSPS, 1.3 mW/MSPS A/D Converter |

| 中文描述: | 8位,20 MSPS的100 MSPS的,1.3毫瓦/ MSPS的A / D转换 |

| 文件页数: | 12/19页 |

| 文件大小: | 572K |

| 代理商: | ADC08100 |

Specification Definitions

APERTURE (SAMPLING) DELAY

is that time required after

the fall of the clock input for the sampling switch to open. The

Sample/Hold circuit effectively stops capturing the input sig-

nal and goes into the “hold” mode t

AD

after the clock goes

low.

APERTURE JITTER

is the variation in aperture delay from

sample to sample. Aperture jitter shows up as input noise.

BOTTOM OFFSET

is the difference between the input volt-

age that just causes the output code to transition to the first

code and the negative reference voltage. Bottom Offset is

defined as E

OB

= V

ZT

– V

RB

, where V

ZT

is the first code

transition input voltage. V

RB

is the lower reference voltage.

Note that this is different from the normal Zero Scale Error.

CLOCK DUTY CYCLE

is the ratio of the time that the clock

waveform is at a logic high to the total time of one clock

period.

DIFFERENTIAL NON-LINEARITY (DNL)

is the measure of

the maximum deviation from the ideal step size of 1 LSB.

Measured at 100 MSPS with a ramp input.

EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE

BITS)

is another method of specifying Signal-to-Noise and

Distortion Ratio, or SINAD. ENOB is defined as (SINAD –

1.76) / 6.02 and says that the converter is equivalent to a

perfect ADC of this (ENOB) number of bits.

FULL POWER BANDWIDTH

is a measure of the frequency

at which the reconstructed output fundamental drops 3 dB

below its low frequency value for a full scale input. The test

is performed with f

equal to 100 kHz plus integer multiples

of f

. The input frequency at which the output is 3 dB

relative to the low frequency input signal is the full power

bandwidth.

FULL-SCALE ERROR

is a measure of how far the last code

transition is from the ideal 1

1

2

LSB below V

RT

and is defined

as:

V

max

+ 1.5 LSB – V

RT

where V

max

is the voltage at which the transition to the

maximum (full scale) code occurs.

INTEGRAL NON-LINEARITY (INL)

is a measure of the

deviation of each individual code from a line drawn from zero

scale (

1

2

LSB below the first code transition) through positive

full scale (

1

2

LSB above the last code transition). The devia-

tion of any given code from this straight line is measured

from the center of that code value. The end point test method

is used. Measured at 100 MSPS with a ramp input.

INTERMODULATION DISTORTION (IMD)

is the creation of

additional spectral components as a result of two sinusoidal

frequencies being applied to theADC input at the same time.

It is defined as the ratio of the power in the second and third

order intermodulation products to the power in one of the

original frequencies. IMD is usually expressed in dBFS.

MISSING CODE

are those output codes that are skipped

and will never appear at the ADC outputs. These codes

cannot be reached with any input value.

OUTPUT DELAY

is the time delay after the rising edge of

the input clock before the data update is present at the

output pins.

OUTPUT HOLD TIME

is the length of time that the output

data is valid after the rise of the input clock.

PIPELINE DELAY (LATENCY)

is the number of clock cycles

between initiation of conversion and when that data is pre-

sented to the output driver stage. New data is available at

every clock cycle, but the data lags the conversion by the

Pipeline Delay plus the Output Delay.

SIGNAL TO NOISE RATIO (SNR)

is the ratio, expressed in

dB, of the rms value of the input signal at the output to the

rms value of the sum of all other spectral components below

one-half the sampling frequency, not including harmonics or

dc.

SIGNAL TO NOISE PLUS DISTORTION (S/(N+D) or

SINAD)

is the ratio, expressed in dB, of the rms value of the

input signal at the output to the rms value of all of the other

spectral components below half the clock frequency, includ-

ing harmonics but excluding dc.

SPURIOUS FREE DYNAMIC RANGE (SFDR)

is the differ-

ence, expressed in dB, between the rms values of the input

signal at the output and the peak spurious signal, where a

spurious signal is any signal present in the output spectrum

that is not present at the input.

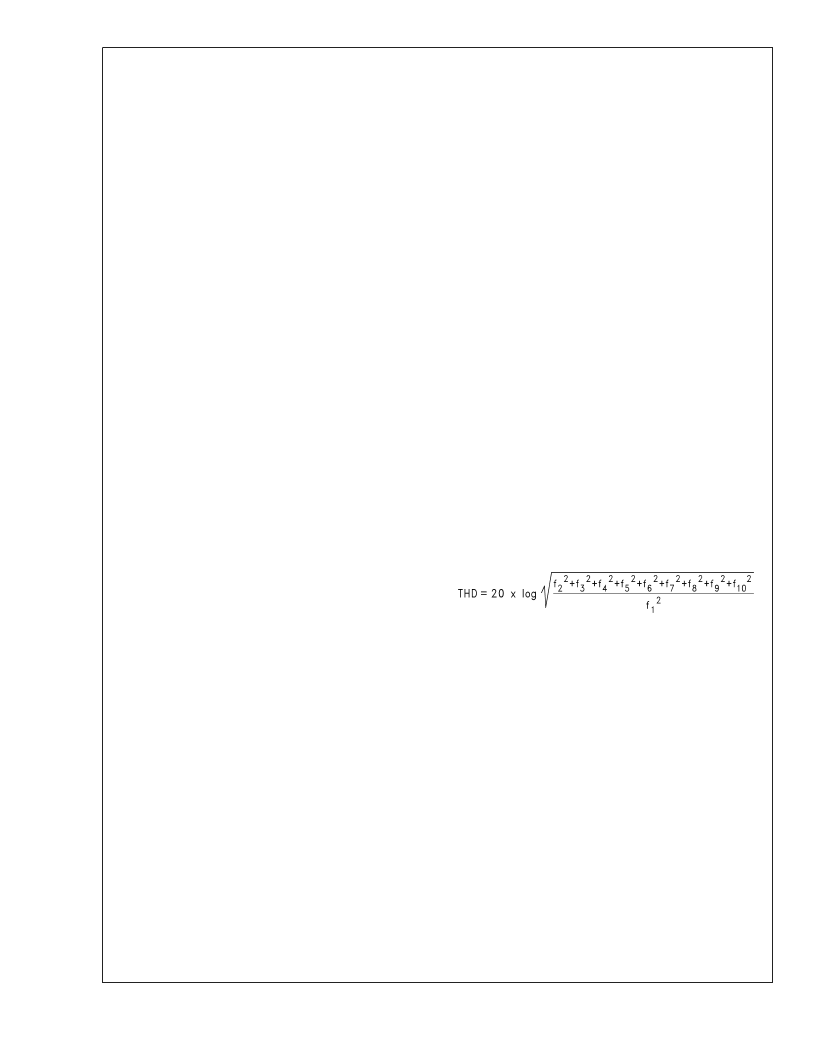

TOTAL HARMONIC DISTORTION (THD)

is the ratio, ex-

pressed in dB, of the total of the first nine harmonic levels at

the output to the level of the fundamental at the output. THD

is calculated as

where F

1

is the RMS power of the fundamental (input)

frequency and f

2

through f

10

is the power in the first 9

harmonics in the output spectrum.

ZERO SCALE OFFSET ERROR

is the error in the input

voltage required to cause the first code transition. It is de-

fined as

V

OFF

= V

ZT

V

RB

where V

ZT

is the first code transition input voltage.

A

www.national.com

12

相关PDF资料 |

PDF描述 |

|---|---|

| ADC08100CIMT | 8-Bit, 20 MSPS to 100 MSPS, 1.3 mW/MSPS A/D Converter |

| ADC08100CIMTX | 8-Bit, 20 MSPS to 100 MSPS, 1.3 mW/MSPS A/D Converter |

| ADC0811 | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| ADC0811BCN | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| ADC0811BCV | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADC08100_08 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit, 20 Msps to 100 Msps, 1.3 mW/Msps A/D Converter |

| ADC081000 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:High Performance, Low Power 8-Bit, 1 GSPS A/D Converter |

| ADC081000_09 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:High Performance, Low Power 8-Bit, 1 GSPS A/D Converter |

| ADC081000CIYB | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADC081000CIYB/NOPB | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。