- 您现在的位置:买卖IC网 > PDF目录20638 > ADE7758ARWZ (Analog Devices Inc)IC ENERGY METERING 3PHASE 24SOIC PDF资料下载

参数资料

| 型号: | ADE7758ARWZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/72页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METERING 3PHASE 24SOIC |

| 标准包装: | 31 |

| 输入阻抗: | 380 千欧 |

| 测量误差: | 0.1% |

| 电压 - 高输入/输出: | 2.4V |

| 电压 - 低输入/输出: | 0.8V |

| 电流 - 电源: | 8mA |

| 电源电压: | 4.75 V ~ 5.25 V |

| 测量仪表类型: | 3 相 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 24-SOIC W |

| 包装: | 管件 |

| 产品目录页面: | 797 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

�� �

�

�

�ADE7758�

�Data� Sheet�

�Parameter� 1,� 2�

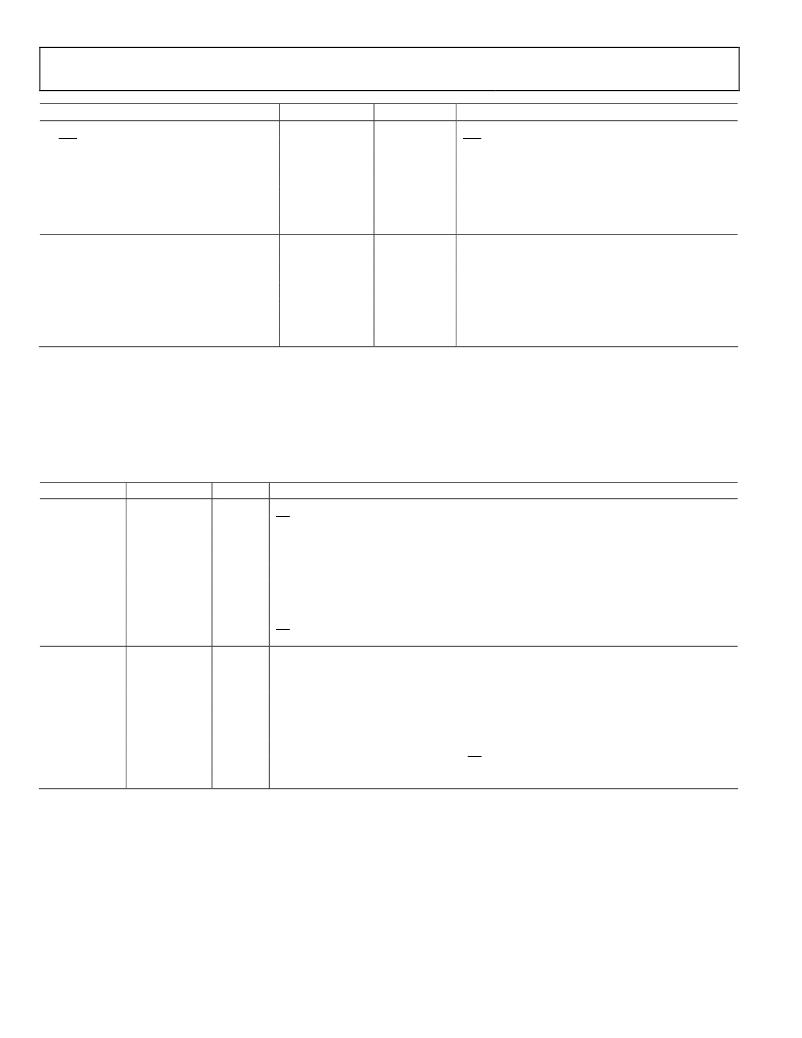

�LOGIC� OUTPUTS�

�IRQ,� DOUT,� and� CLKOUT�

�Output� High� Voltage,� V� OH�

�Output� Low� Voltage,� V� OL�

�Specification�

�4�

�0.4�

�Unit�

�V� min�

�V� max�

�Test� Conditions/Comments�

�DVDD� =� 5� V� ±� 5%�

�IRQ� is� open-drain,� 10� k� pull-up� resistor�

�I� SOURCE� =� 5� mA�

�I� SINK� =� 1� mA�

�APCF� and� VARCF�

�Output� High� Voltage,� V� OH�

�Output� Low� Voltage,� V� OL�

�POWER� SUPPLY�

�AVDD�

�DVDD�

�AI� DD�

�DI� DD�

�4�

�1�

�4.75�

�5.25�

�4.75�

�5.25�

�8�

�13�

�V� min�

�V� max�

�V� min�

�V� max�

�V� min�

�V� max�

�mA� max�

�mA� max�

�I� SOURCE� =� 8� mA�

�I� SINK� =� 5� mA�

�For� specified� performance�

�5� V� ?� 5%�

�5� V� +� 5%�

�5� V� ?� 5%�

�5� V� +� 5%�

�Typically� 5� mA�

�Typically� 9� mA�

�1�

�2�

�3�

�See� the� Typical� Performance� Characteristics.�

�See� the� Terminology� section� for� a� definition� of� the� parameters.�

�See� the� Analog� Inputs� section.�

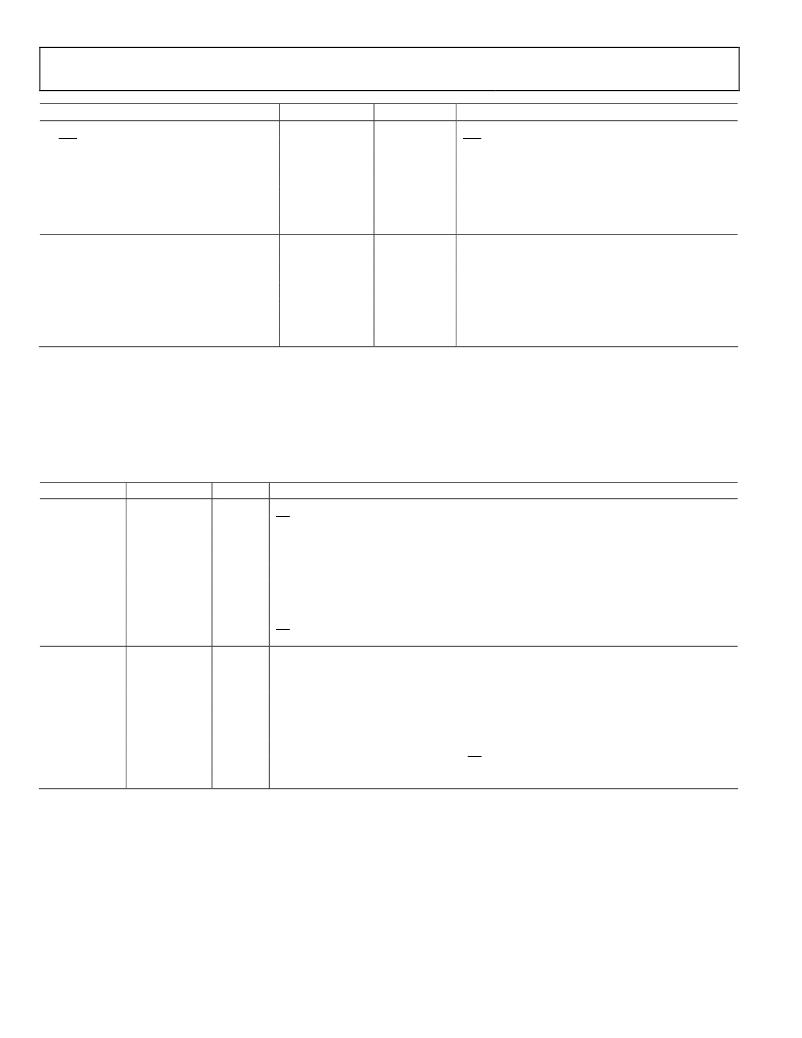

�TIMING� CHARACTERISTICS�

�AVDD� =� DVDD� =� 5� V� ±� 5%,� AGND� =� DGND� =� 0� V,� on-chip� reference,� CLKIN� =� 10� MHz� XTAL,� T� MIN� to� T� MAX� =� ?40°C� to� +85°C.�

�Table� 2.�

�Parameter� 1,� 2�

�Specification�

�Unit�

�Test� Conditions/Comments�

�WRITE� TIMING�

�t� 1�

�t� 2�

�t� 3�

�t� 4�

�t� 5�

�t� 6�

�t� 7�

�t� 8�

�50�

�50�

�50�

�10�

�5�

�1200�

�400�

�100�

�ns� (min)�

�ns� (min)�

�ns� (min)�

�ns� (min)�

�ns� (min)�

�ns� (min)�

�ns� (min)�

�ns� (min)�

�CS� falling� edge� to� first� SCLK� falling� edge�

�SCLK� logic� high� pulse� width�

�SCLK� logic� low� pulse� width�

�Valid� data� setup� time� before� falling� edge� of� SCLK�

�Data� hold� time� after� SCLK� falling� edge�

�Minimum� time� between� the� end� of� data� byte� transfers�

�Minimum� time� between� byte� transfers� during� a� serial� write�

�CS� hold� time� after� SCLK� falling� edge�

�READ� TIMING�

�t� 9� 3�

�4�

�μs� (min)�

�Minimum� time� between� read� command� (that� is,� a� write� to� communication� register)� and�

�data� read�

�t� 10�

�t� 11� 4�

�t� 12� 5�

�t� 135�

�50�

�30�

�100�

�10�

�100�

�10�

�ns� (min)�

�ns� (min)�

�ns� (max)�

�ns� (min)�

�ns� (max)�

�ns� (min)�

�Minimum� time� between� data� byte� transfers� during� a� multibyte� read�

�Data� access� time� after� SCLK� rising� edge� following� a� write� to� the� communications� register�

�Bus� relinquish� time� after� falling� edge� of� SCLK�

�Bus� relinquish� time� after� rising� edge� of� CS�

�1�

�2�

�3�

�4�

�5�

�Sample� tested� during� initial� release� and� after� any� redesign� or� process� change� that� may� affect� this� parameter.� All� input� signals� are� specified� with� tr� =� tf� =� 5� ns� (10%� to�

�90%)� and� timed� from� a� voltage� level� of� 1.6� V.�

�See� the� timing� diagrams� in� Figure� 3� and� Figure� 4� and� the� Serial� Interface� section.�

�Minimum� time� between� read� command� and� data� read� for� all� registers� except� waveform� register,� which� is� t� 9� =� 500� ns� min.�

�Measured� with� the� load� circuit� in� Figure� 2� and� defined� as� the� time� required� for� the� output� to� cross� 0.8� V� or� 2.4� V.�

�Derived� from� the� measured� time� taken� by� the� data� outputs� to� change� 0.5� V� when� loaded� with� the� circuit� in� Figure� 2.� The� measured� number� is� then� extrapolated� back�

�to� remove� the� effects� of� charging� or� discharging� the� 50� pF� capacitor.� This� means� that� the� time� quoted� here� is� the� true� bus� relinquish� time� of� the� part� and� is�

�independent� of� the� bus� loading.�

�Rev.� E� |� Page� 6� of� 72�

�相关PDF资料 |

PDF描述 |

|---|---|

| VI-J60-CX-F2 | CONVERTER MOD DC/DC 5V 75W |

| ADE7754ARZ | IC ENERGY METERING 3PHASE 24SOIC |

| MAX8631YETI+ | IC LED DRVR WHITE BCKLGT 28-TQFN |

| EBC15DCMI-S288 | CONN EDGECARD 30POS .100 EXTEND |

| ISL6605IRZ-T | IC MOSFET DRVR SYNC BUCK 8-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADE7758ARWZ | 制造商:Analog Devices 功能描述:ENERGY METERING IC 制造商:Analog Devices 功能描述:IC, POLY-PHASE ENERGY METERING, SOIC-24 |

| ADE7758ARWZ | 制造商:Analog Devices 功能描述:IC ENERGY METER 3 PHASE SOIC-24 |

| ADE7758ARWZRL | 功能描述:IC ENERGY METERING 3PHASE 24SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

| ADE7759 | 制造商:AD 制造商全称:Analog Devices 功能描述:Active Energy Metering IC with di/dt Sensor Interface |

| ADE7759ARS | 功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

发布紧急采购,3分钟左右您将得到回复。