- 您现在的位置:买卖IC网 > PDF目录373996 > ADM1066ACP-U3 (ANALOG DEVICES INC) Multisupply Supervisor/Sequencer with Margining Control and Auxiliary ADC Inputs PDF资料下载

参数资料

| 型号: | ADM1066ACP-U3 |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 电源管理 |

| 英文描述: | Multisupply Supervisor/Sequencer with Margining Control and Auxiliary ADC Inputs |

| 中文描述: | 2-CHANNEL POWER SUPPLY SUPPORT CKT, QCC40 |

| 封装: | 6 X 6 MM, MO-220-VVJJD-2, LFCSP-40 |

| 文件页数: | 26/32页 |

| 文件大小: | 861K |

| 代理商: | ADM1066ACP-U3 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页

ADM1066

The device also has several identification registers (read-only),

which can be read across the SMBus. Table 10 lists these registers

with their values and functions.

Table 10. Identification Register Values and Functions

Name

Address

Value

MANID

0xF4

0x41

Rev. 0 | Page 26 of 32

Function

Manufacturer ID for Analog

Devices

Silicon revision

S/w brand

S/w brand

REVID

MARK1

MARK2

0xF5

0xF6

0xF7

0x00

0x00

0x00

General SMBus Timing

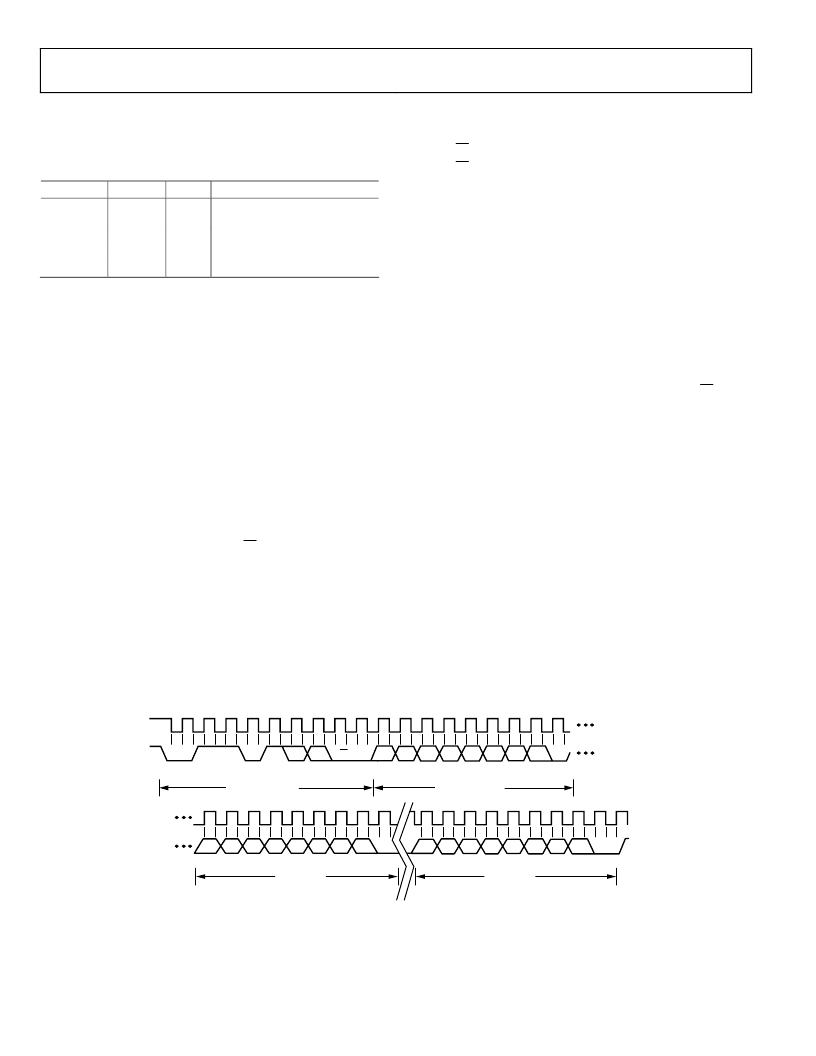

Figure 36, Figure 37, and Figure 38 are timing diagrams for

general read and write operations using the SMBus. The SMBus

specification defines specific conditions for different types of

read and write operations, which are discussed in the Write

Operations and Read Operations sections.

The general SMBus protocol operates as follows:

1.

The master initiates data transfer by establishing a start

condition, defined as a high-to-low transition on the serial

data-line SDA, while the serial clock-line SCL remains

high. This indicates that a data stream follows. All slave

peripherals connected to the serial bus respond to the start

condition and shift in the next 8 bits, consisting of a 7-bit

slave address (MSB first) plus a R/W bit. This bit deter-

mines the direction of the data transfer, that is, whether

data is written to or read from the slave device (0 = write,

1 = read).

The peripheral whose address corresponds to the transmit-

ted address responds by pulling the data line low during

the low period before the ninth clock pulse, known as the

acknowledge bit, and holding it low during the high period

of this clock pulse.

All other devices on the bus remain idle while the selected

device waits for data to be read from or written to it. If the

R/W bit is a 0, the master writes to the slave device. If the

R/W bit is a 1, the master reads from the slave device.

2.

Data is sent over the serial bus in sequences of nine clock

pulses, eight bits of data followed by an acknowledge bit

from the slave device. Data transitions on the data line

must occur during the low period of the clock signal and

remain stable during the high period, because a low-to-

high transition when the clock is high might be interpreted

as a stop signal. If the operation is a write operation, the

first data byte after the slave address is a command byte.

This tells the slave device what to expect next. It might be

an instruction telling the slave device to expect a block

write, or it might simply be a register address that tells the

slave where subsequent data is to be written. Because data

can flow in only one direction, as defined by the R/W bit,

sending a command to a slave device during a read

operation is not possible. Before a read operation, it might

be necessary to perform a write operation to tell the slave

what sort of read operation to expect and/or the address

from which data is to be read.

3.

When all data bytes have been read or written, stop condi-

tions are established. In write mode, the master pulls the

data line high during the 10th clock pulse to assert a stop

condition. In read mode, the master device releases the

SDA line during the low period before the ninth clock

pulse, but the slave device does not pull it low. This is

known as no acknowledge. The master then takes the data

line low during the low period before the tenth clock pulse,

then high during the tenth clock pulse to assert a stop

condition.

0

1

9

9

1

1

9

1

9

START BY

MASTER

ACK. BY

SLAVE

ACK. BY

SLAVE

ACK. BY

SLAVE

ACK. BY

SLAVE

FRAME 2

COMMAND CODE

FRAME 1

SLAVE ADDRESS

FRAME N

DATA BYTE

FRAME 3

DATA BYTE

SCL

SDA

R/W

STOP

BY

MASTER

SCL

(CONTINUED)

SDA

(CONTINUED)

D7

A0

A1

1

1

1

0

0

D6

D5

D4

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

Figure 36. General SMBus Write Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| ADM1066 | Multisupply Supervisor/Sequencer with Margining Control and Auxiliary ADC Inputs |

| ADM1066ASU | Multisupply Supervisor/Sequencer with Margining Control and Auxiliary ADC Inputs |

| ADM1069 | SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

| ADM1069ACP | SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

| ADM1069ACP-REEL | SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADM1066ACPZ | 功能描述:IC SEQUENCER/SUPERVISOR 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:Super Sequencer® 其它有关文件:STM6717 View All Specifications 标准包装:1 系列:- 类型:多压监控器 监视电压数目:2 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:1.11V,3.075V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:Digi-Reel® 产品目录页面:1194 (CN2011-ZH PDF) 其它名称:497-7019-6 |

| ADM1066ACPZ-REEL | 功能描述:IC SEQUENCER/SUPERVISOR 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:Super Sequencer® 标准包装:1 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:高有效 复位超时:- 电压 - 阀值:1.8V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:6-TSOP(0.059",1.50mm 宽)5 引线 供应商设备封装:5-TSOP 包装:剪切带 (CT) 其它名称:NCP301HSN18T1GOSCT |

| ADM1066ACPZ-REEL7 | 功能描述:IC SEQUENCER/SUPERVISOR 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:Super Sequencer® 标准包装:1 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:高有效 复位超时:- 电压 - 阀值:1.8V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:6-TSOP(0.059",1.50mm 宽)5 引线 供应商设备封装:5-TSOP 包装:剪切带 (CT) 其它名称:NCP301HSN18T1GOSCT |

| ADM1066ARTZ | 制造商:Analog Devices 功能描述:SUPER SEQUENCER - Tape and Reel |

| ADM1066ASU | 制造商:Analog Devices 功能描述:Volt Supervisor Sequencer 2.7V to 5.4V 48-Pin TQFP |

发布紧急采购,3分钟左右您将得到回复。