- 您现在的位置:买卖IC网 > PDF目录15586 > ADM6320CZ27ARJZ-R7 (Analog Devices Inc)IC SUPERVISOR MANUAL RST SOT23-5 PDF资料下载

参数资料

| 型号: | ADM6320CZ27ARJZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/16页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISOR MANUAL RST SOT23-5 |

| 标准包装: | 1 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 最小为 140 ms |

| 电压 - 阀值: | 2.7V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | SC-74A,SOT-753 |

| 供应商设备封装: | SOT-23-5 |

| 包装: | 标准包装 |

| 其它名称: | ADM6320CZ27ARJZ-R7DKR |

�� ��

��

��

��Data� Sheet�

�ADM6316/ADM6317/ADM6318/ADM6319/ADM6320/ADM6321/ADM6322�

�CIRCUIT� DESCRIPTION�

�The� ADM6316/ADM6317/ADM6318/ADM6319/ADM6320/�

�ADM6321/ADM6322� provide� microprocessor� supply� voltage�

�supervision� by� controlling� the� microprocessor’s� reset� input.� Code�

�execution� errors� are� avoided� during� power-up,� power-down,�

�and� brownout� conditions� by� asserting� a� reset� signal� when� the�

�supply� voltage� is� below� a� preset� threshold� and� by� allowing�

�supply� voltage� stabilization� with� a� fixed� timeout� reset� pulse�

�after� the� supply� voltage� rises� above� the� threshold.� In� addition,�

�problems� with� microprocessor� code� execution� can� be� monitored�

�and� corrected� with� a� watchdog� timer� (ADM6316/ADM6317/�

�ADM6318/ADM6320/ADM6321).� If� the� user� detects� a� problem�

�with� the� system’s� operation,� a� manual� reset� input� is� available�

�(ADM6316/ADM6317/ADM6319/ADM6320/ADM6322)� to�

�reset� the� microprocessor,� for� example,� by� means� of� an� external�

�push� button.�

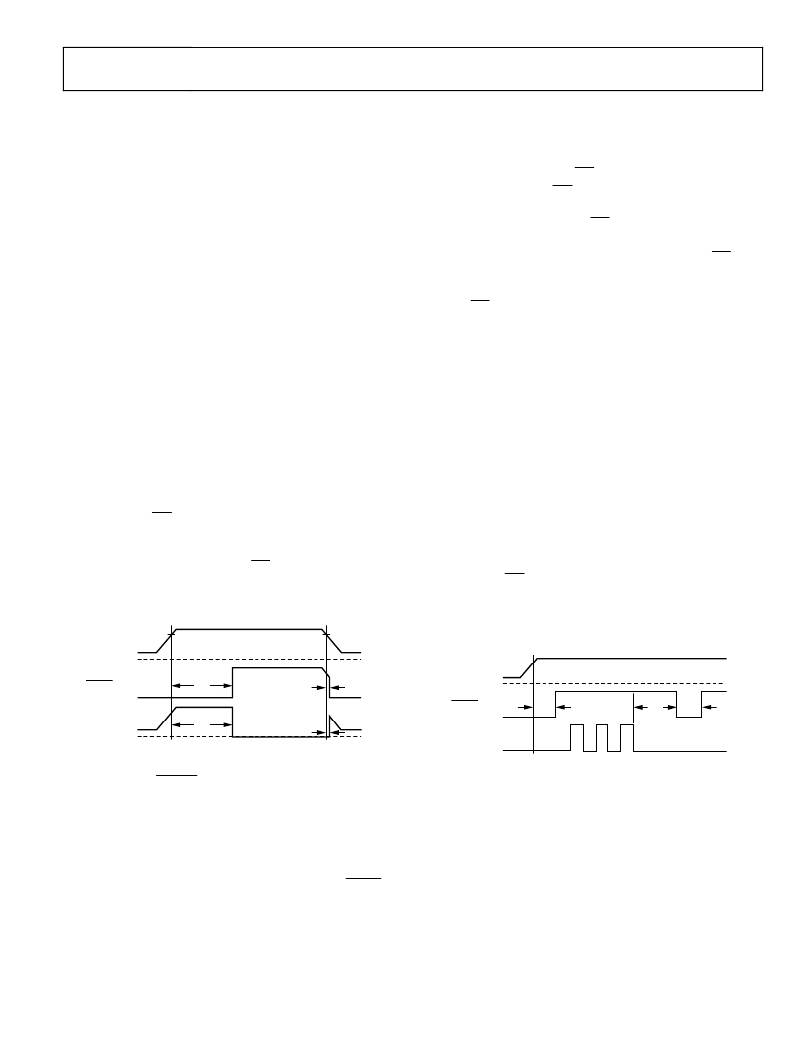

�RESET� OUTPUT�

�The� ADM6316� features� an� active-low� push-pull� reset� output,�

�while� the� ADM6317/ADM6321/ADM6322� have� active-high�

�push-pull� reset� outputs.� The� ADM6318/ADM6319� feature� dual�

�active-low� and� active-high� push-pull� reset� outputs.� For� active-�

�low� and� active-high� outputs,� the� reset� signal� is� guaranteed� to� be�

�logic� low� and� logic� high,� respectively,� for� V� CC� down� to� 1� V.�

�The� reset� output� is� asserted� when� V� CC� is� below� the� reset� thresh-�

�old� (V� TH� ),� when� MR� is� driven� low,� or� when� WDI� is� not� serviced�

�within� the� watchdog� timeout� period� (t� WD� ).� Reset� remains� asserted�

�for� the� duration� of� the� reset� active� timeout� period� (t� RP� )� after� V� CC�

�rises� above� the� reset� threshold,� after� MR� transitions� from� low� to�

�high,� or� after� the� watchdog� timer� times� out.� Figure� 17� illustrates�

�the� behavior� of� the� reset� outputs.�

�MANUAL� RESET� INPUT�

�The� ADM6316/ADM6317/ADM6319/ADM6320/ADM6322�

�feature� a� manual� reset� input� (MR),� which� when� driven� low,� asserts�

�the� reset� output.� When� MR� transitions� from� low� to� high,� reset�

�remains� asserted� for� the� duration� of� the� reset� active� timeout�

�period� before� deasserting.� The� MR� input� has� a� 52� kΩ,� internal�

�pull-up� so� that� the� input� is� always� high� when� unconnected.� An�

�external� push-button� switch� can� be� connected� between� MR� and�

�ground� so� that� the� user� can� generate� a� reset.� Debounce� circuitry�

�for� this� purpose� is� integrated� on� chip.� Noise� immunity� is� provided�

�on� the� MR� input,� and� fast,� negative-going� transients� of� up� to�

�100� ns� (typical)� are� ignored.� A� 0.1� μF� capacitor� between� MR� and�

�ground� provides� additional� noise� immunity.�

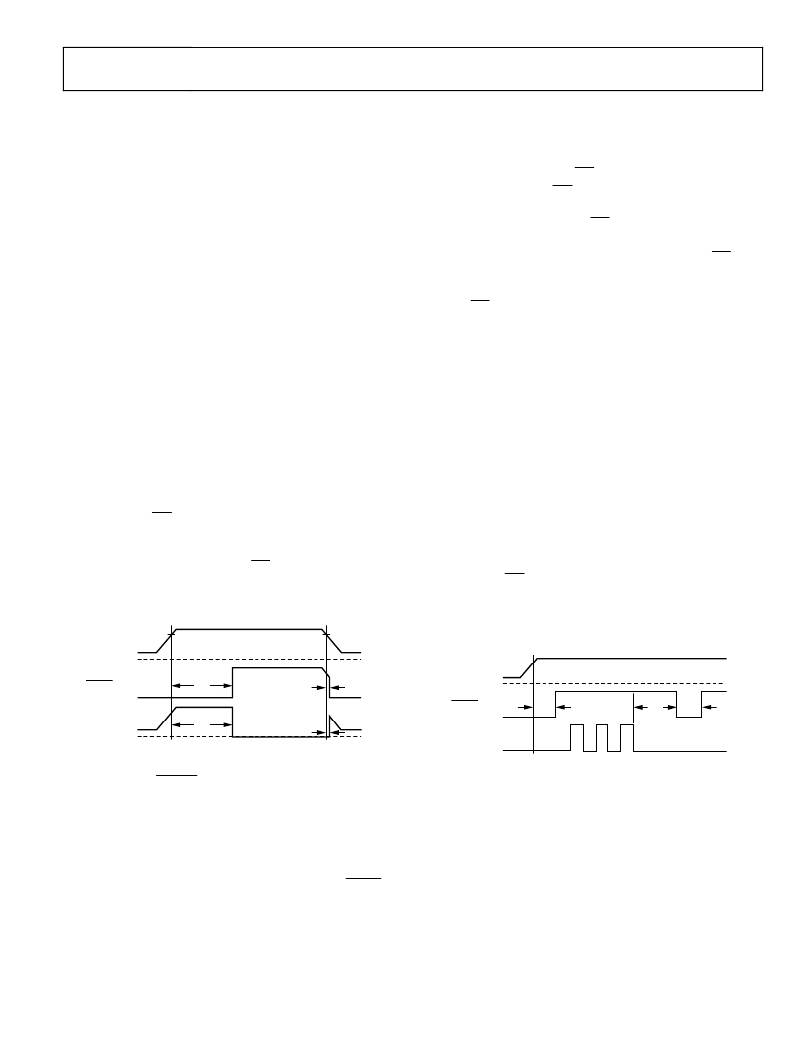

�WATCHDOG� INPUT�

�The� ADM6316/ADM6317/ADM6318/ADM6320/ADM6321�

�feature� a� watchdog� timer� that� monitors� microprocessor� activity.�

�A� timer� circuit� is� cleared� with� every� low-to-high� or� high-to-low�

�logic� transition� on� the� watchdog� input� pin� (WDI),� which� detects�

�pulses� as� short� as� 50� ns.� If� the� timer� counts� through� the� preset�

�watchdog� timeout� period� (t� WD� ),� reset� is� asserted.� The� micro-�

�processor� is� required� to� toggle� the� WDI� pin� to� avoid� being� reset.�

�Failure� of� the� microprocessor� to� toggle� WDI� within� the� timeout�

�period,� therefore,� indicates� a� code� execution� error,� and� the� reset�

�pulse� generated� restarts� the� microprocessor� in� a� known� state.�

�As� well� as� logic� transitions� on� WDI,� the� watchdog� timer� is� also�

�cleared� by� a� reset� assertion� due� to� an� undervoltage� condition� on�

�V� CC� or� due� to� MR� being� pulled� low.� When� reset� is� asserted,� the�

�watchdog� timer� is� cleared� and� does� not� begin� counting� again�

�until� reset� deassserts.� The� watchdog� timer� can� be� disabled� by�

�V� CC�

�RESET�

�V� CC�

�1V�

�0V�

�V� CC�

�V� TH�

�t� RP�

�V� TH�

�t� RD�

�leaving� WDI� floating� or� by� three-stating� the� WDI� driver.�

�V� CC�

�V� TH�

�V� CC�

�1V�

�0V�

�RESET�

�0V�

�V� CC�

�1V�

�0V�

�t� RP�

�t� RD�

�RESET�

�WDI�

�V� CC�

�0V�

�V� CC�

�t� RP�

�t� WD�

�t� RP�

�Figure� 17.� Reset� Timing� Diagram�

�0V�

�Figure� 18.� Watchdog� Timing� Diagram�

�OPEN-DRAIN� RESET� OUTPUT�

�The� ADM6320/ADM6321/ADM6322� have� an� active-low,� open-�

�drain� reset� output.� This� output� structure� requires� an� external�

�pull-up� resistor� to� connect� the� reset� output� to� a� voltage� rail� no�

�higher� than� 6� V.� The� resistor� should� comply� with� the� micro-�

�processor’s� logic� low� and� logic� high� voltage� level� requirements�

�while� supplying� input� current� and� leakage� paths� on� the� RESET�

�line.� A� 10� k� resistor� is� adequate� in� most� situations.�

�Rev.� F� |� Page� 9� of� 16�

�相关PDF资料 |

PDF描述 |

|---|---|

| H4BXG-10105-N1-ND | JUMPER-H9991TR/A3047N/X 5" |

| MAX6442KAMSSD7+T | IC BATTERY MON DUAL SOT23-8 |

| VE-B6P-EY-F2 | CONVERTER MOD DC/DC 13.8V 50W |

| GEC28DRYS-S93 | CONN EDGECARD 56POS DIP .100 SLD |

| V48C5E100BF2 | CONVERTER MOD DC/DC 5V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADM6320CZ29-ARJ-RL7 | 制造商:AD 制造商全称:Analog Devices 功能描述:Supervisory Circuits with Watchdog and Manual Reset in 5-Lead SOT-23 |

| ADM6320CZ29ARJ-RL7 | 功能描述:IC SUPERVISOR WATCHDOG SOT23-5 RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:双向 复位:低有效 复位超时:最小为 140 ms 电压 - 阀值:4.63V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:TO-253-4,TO-253AA 供应商设备封装:SOT-143-4 包装:剪切带 (CT) 产品目录页面:1414 (CN2011-ZH PDF) 其它名称:MAX6314US46D3+TCT |

| ADM6320CZ29-ARJZ-R7 | 制造商:AD 制造商全称:Analog Devices 功能描述:Supervisory Circuits with Watchdog and Manual Reset in 5-Lead SOT-23 |

| ADM6320CZ29ARJZ-R7 | 功能描述:IC SUPERVISOR WATCHDOG SOT23-5 RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极,开路漏极 复位:高有效/低有效 复位超时:最小为 250 ms 电压 - 阀值:4.37V,4.62V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:管件 产品目录页面:1337 (CN2011-ZH PDF) |

| ADM6320xxxARJ-RL7 | 制造商:AD 制造商全称:Analog Devices 功能描述:Supervisory Circuits with Watchdog |

发布紧急采购,3分钟左右您将得到回复。