- 您现在的位置:买卖IC网 > PDF目录17093 > ADS1244EVM (Texas Instruments)EVALUATION MODULE FOR ADS1244 PDF资料下载

参数资料

| 型号: | ADS1244EVM |

| 厂商: | Texas Instruments |

| 文件页数: | 3/24页 |

| 文件大小: | 0K |

| 描述: | EVALUATION MODULE FOR ADS1244 |

| 产品培训模块: | Data Converter Basics |

| 视频文件: | Nuts and Bolts of the Delta-Sigma Converter |

| 标准包装: | 1 |

| ADC 的数量: | 2 |

| 位数: | 24 |

| 采样率(每秒): | 15 |

| 数据接口: | 串行 |

| 输入范围: | 0 ~ 5 V |

| 在以下条件下的电源(标准): | 150mW @ 500kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | ADS1244 |

| 已供物品: | 板 |

| 产品目录页面: | 889 (CN2011-ZH PDF) |

| 相关产品: | ADS1244IDGSTG4-ND - IC ADC LP CONVERT 24BIT 10-MSOP ADS1244IDGSRG4-ND - IC ADC LP CONVERT 24BIT 10-MSOP ADS1244IDGSR-ND - IC ADC LP CONVERT 24BIT 10-MSOP 296-14003-6-ND - IC ADC LP 24-BIT 10-MSOP 296-14003-2-ND - IC ADC LP 24-BIT 10-MSOP 296-14003-1-ND - IC ADC LP 24-BIT 10-MSOP |

| 其它名称: | 296-18359 |

ADS1244

11

SBAS273

www.ti.com

DATA RETRIEVAL

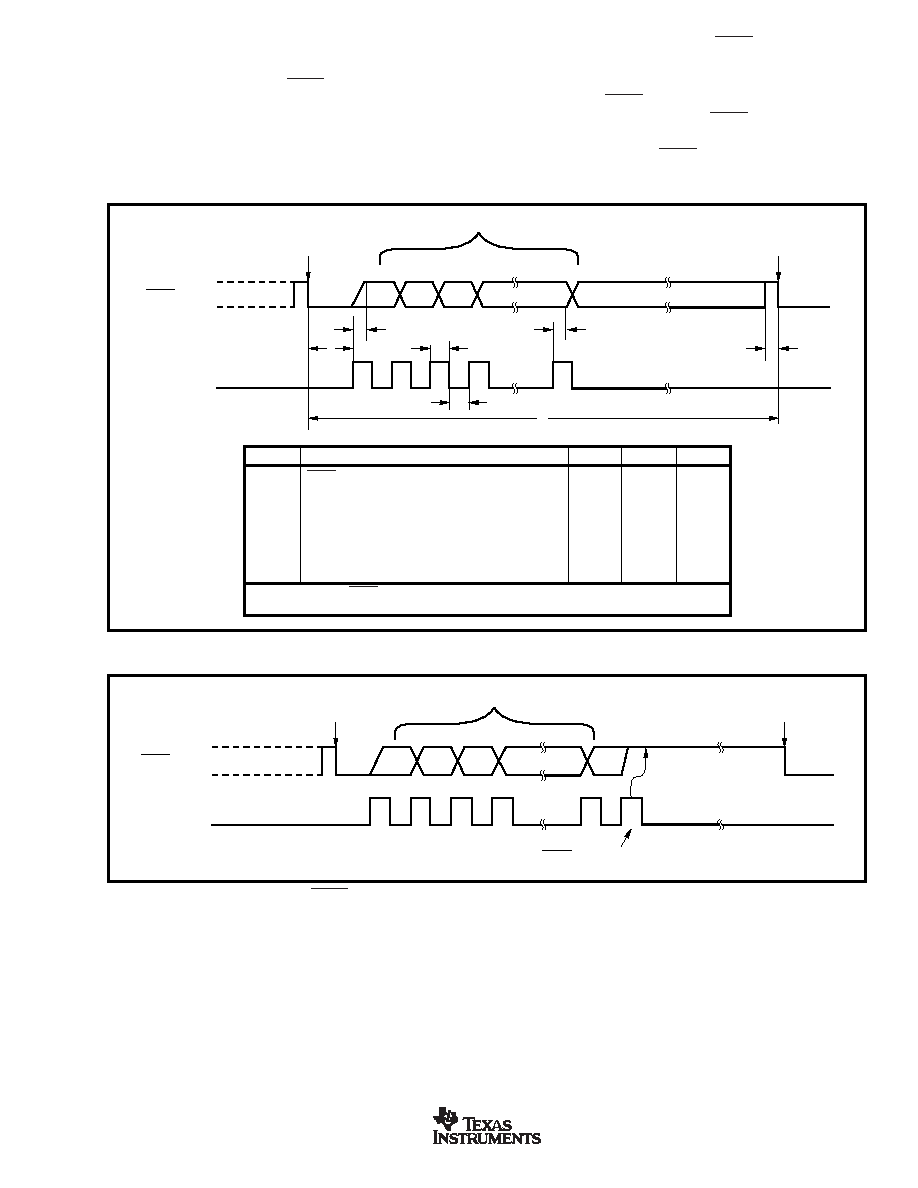

The ADS1244 continuously converts the analog input signal.

To retrieve data, wait until DRDY/DOUT goes LOW, as

shown in Figure 12. After this occurs, begin shifting out the

data by applying SCLKs. Data is shifted out Most Significant

Bit (MSB) first. It is not required to shift out all the 24 bits of

data, but the data must be retrieved before the new data is

updated (see t3) or else it will be overwritten. Avoid data

retrieval during the update period. DRDY/DOUT will remain

at the state of the last bit shifted out until it is taken HIGH (see

t7), indicating that new data is being updated.

To avoid having DRDY/DOUT remain in the state of the last

bit, shift a 25th SCLK to force DRDY/DOUT HIGH, see

Figure 13. This technique is useful when a host controlling

the ADS1244 is polling DRDY/DOUT to determine when

data is ready.

FIGURE 12. Data Retrieval Timing.

DRDY/DOUT

23

22

21

124

0

LSB

MSB

Data

Data is ready.

SCLK

t

3

t

8

t

4

t

4

t

7

New data is ready.

t

5

t

6

FIGURE 13. Data Retrieval with DRDY/DOUT Forced HIGH Afterwards.

23

124

25

22

21

0

Data

25th SCLK to force DRDY/DOUT HIGH.

Data is ready.

New data is ready.

DRDY/DOUT

SCLK

SYMBOL

DESCRIPTION

MIN

MAX

UNITS

t3

DRDY/DOUT LOW to first SCLK rising edge.

0

ns

t4

SCLK positive or negative pulse width.

100

ns

t5(1)

SCLK rising edge to new data bit valid:

50

ns

propagation delay.

t6

SCLK rising edge to old data bit valid: hold time.

0

ns

t7(2)

Data updating, no read back allowed.

152

s

t8(2)

Conversion time (1/data rate).

66.667

ms

NOTES: (1) Load on DRDY/DOUT = 20pF || 100k

. (2) Values given for f

CLK = 2.4576MHz. For different

CLK frequencies, scale proportional to CLK period. For example, for fCLK = 4.9152MHz, t8 → 33.333ms.

相关PDF资料 |

PDF描述 |

|---|---|

| GCM18DCMT-S288 | CONN EDGECARD 36POS .156 EXTEND |

| 0150150239 | CABLE FLAT FLEX 39POS .3MM 2" |

| SDR-L | SCOTCH CODE REFILL L |

| ESM15DRSN-S288 | CONN EDGECARD 30POS .156 EXTEND |

| VE-JWD-EZ | CONVERTER MOD DC/DC 85V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS1244-EVM | 制造商:BB 制造商全称:BB 功能描述:Low-Power, 24-Bit ANALOG-TO-DIGITAL CONVERTER |

| ADS1244IDGSR | 功能描述:模数转换器 - ADC 24-Bit Delta-Sigma 15SPS w/50-60Hz rej RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS1244IDGSRG4 | 功能描述:模数转换器 - ADC 24-Bit Delta-Sigma 15SPS w/50-60Hz rej RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS1244IDGST | 功能描述:模数转换器 - ADC 24-Bit Delta-Sigma 15SPS w/50-60Hz rej RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS1244IDGSTG4 | 功能描述:模数转换器 - ADC 24-Bit Delta-Sigma 15SPS w/50-60Hz rej RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。