- 您现在的位置:买卖IC网 > PDF目录223311 > ADS8382IBRHPT (TEXAS INSTRUMENTS INC) 1-CH 18-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PQCC28 PDF资料下载

参数资料

| 型号: | ADS8382IBRHPT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 1-CH 18-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PQCC28 |

| 封装: | 6 X 6 MM, GREEN, PLASTIC, QFN-28 |

| 文件页数: | 8/35页 |

| 文件大小: | 1416K |

| 代理商: | ADS8382IBRHPT |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

www.ti.com

D

Q

LATCH

CONVST

CS

CONVST_QUAL

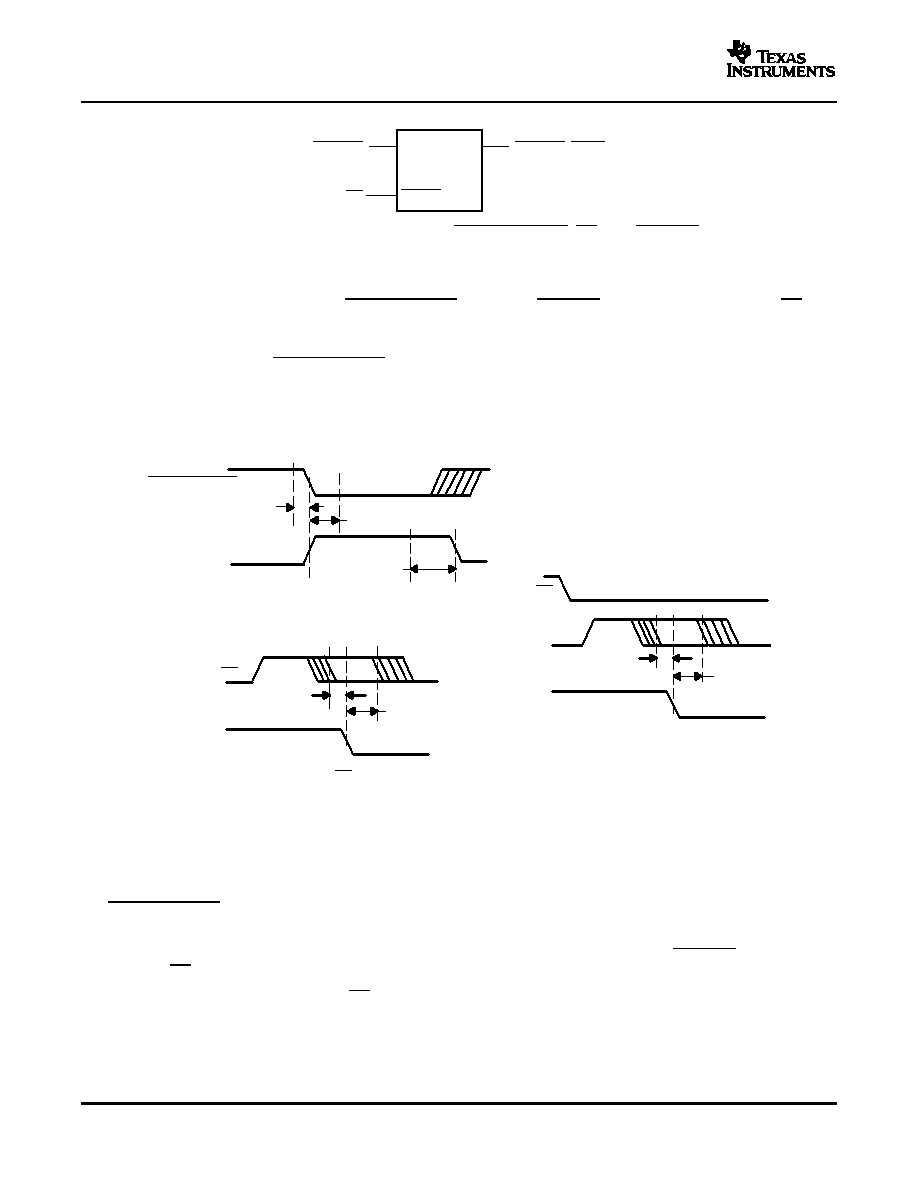

TIMING DIAGRAMS

BUSY

CONVST_QUAL

tquiet1

tquiet2

tquiet3

Quiet Zones

tsu2

th2

CS

No Read Zone (CS Initiated)

tsu3

th8

CS

FS

No Read Zone (FS Initiated)

CONVERSION AND SAMPLING

ADS8382

SLAS416B – JUNE 2004 – REVISED NOVEMBER 2004

Figure 41. Relationship Between CONVST_QUAL, CS, and CONVST

In the following descriptions, the signal CONVST_QUAL represents CONVST latched by a low value on CS (see

To avoid performance degradation, there are three quiet zones to be observed (tquiet1 and tquiet2 are zones before

and after the falling edge of CONVST_QUAL while tquiet3 is a time zone before the falling edge of BUSY) where

there should be no I/O activities. Interface control signals, including the serial clock should remain steady. Typical

degradation in performance if these quiet zones are not observed is depicted in the specifications section.

To avoid data loss a read operation should not start around the BUSY falling edge. This is constrained by tsu2,

tsu3, th2, and th8.

Figure 42. Quiet Zones and No-Read Zones

1. Convert start command:

The device enters the conversion phase from the sampling phase when a falling edge is detected on

CONVST_QUAL. This is shown in Figure 43, Figure 44, and Figure 45.

2. Sample (acquisition) start command:

The device starts sampling from the wait/nap state or at the end of a conversion if CONVST is detected as

high and CS as low. This is shown in Figure 43, Figure 44, and Figure 45.

Maintaining this condition (holding CS low) when the device has just finished a conversion (as shown in

Figure 43) takes the device immediately into the sampling phase after the conversion phase (back-to-back

conversion) and hence achieves the maximum throughput. Otherwise, the device enters the wait state or the

nap state.

16

相关PDF资料 |

PDF描述 |

|---|---|

| ADS8422IBPFBR | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQFP48 |

| ADSP-2189NBSTZ-320 | 16-Bit, 80MIPS, 1.8V, 2 Serial Ports, Host Port, 192KB RAM; Package: 100 ld LQFP; No of Pins: 100; Temperature Range: Ind |

| ADSP-2189NKCAZ-320 | 16-Bit, 80MIPS, 1.8V, 2 Serial Ports, Host Port, 192KB RAM; Package: CHIP SCALE BGA; No of Pins: 144; Temperature Range: Comm. |

| ADSP-2189NKSTZ-320 | 16-Bit, 80MIPS, 1.8V, 2 Serial Ports, Host Port, 192KB RAM; Package: 100 ld LQFP; No of Pins: 100; Temperature Range: Comm. |

| ADSP-2191MBCAZ-140 | 16-bit Fixed-Point DSP, 160 MIPS, 160K bytes RAM; Package: CHIP SCALE BGA; No of Pins: 144; Temperature Range: Ind |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS8382IBRHPTG4 | 功能描述:模数转换器 - ADC 18-Bit 600KSPS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS8382IRHPR | 功能描述:模数转换器 - ADC 18-Bit 600KSPS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS8382IRHPRG4 | 功能描述:模数转换器 - ADC 18-Bit 600KSPS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS8382IRHPT | 功能描述:模数转换器 - ADC 18-Bit 600KSPS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS8382IRHPTG4 | 功能描述:模数转换器 - ADC 18-Bit 600KSPS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。