- 您现在的位置:买卖IC网 > PDF目录19370 > ADSP-21060LKSZ-133 (Analog Devices Inc)IC DSP CONTROLLER 32BIT 240-MQFP PDF资料下载

参数资料

| 型号: | ADSP-21060LKSZ-133 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/64页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 32BIT 240-MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 主机接口,连接端口,串行端口 |

| 时钟速率: | 33MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 512kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 3.30V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 240-BFQFP 裸露焊盘 |

| 供应商设备封装: | 240-MQFP-EP(32x32) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Rev. F

|

Page 34 of 64

|

March 2008

ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

Three-State Timing—Bus Master/ Bus Slave

These specifications show how the memory interface is disabled

(stops driving) or enabled (resumes driving) relative to CLKIN

and the SBTS pin. This timing is applicable to bus master transi-

tion cycles (BTC) and host transition cycles (HTC) as well as the

SBTS pin.

Table 21. Three-State Timing—Bus Master, Bus Slave

5 V and 3.3 V

Unit

Parameter

Min

Max

Timing Requirements

tSTSCK

SBTS Setup Before CLKIN

12 + DT/2

ns

tHTSCK

SBTS Hold Before CLKIN

6 + DT/2

ns

Switching Characteristics

tMIENA

Address/Select Enable After CLKIN1

–1.5 – DT/8

ns

tMIENS

Strobes Enable After CLKIN2

–1.5 – DT/8

ns

tMIENHG

HBG Enable After CLKIN

–1.5 – DT/8

ns

tMITRA

Address/Select Disable After CLKIN3

0 – DT/4

ns

tMITRS

Strobes Disable After CLKIN2

1.5 – DT/4

ns

tMITRHG

HBG Disable After CLKIN

2.0 – DT/4

ns

tDATEN

Data Enable After CLKIN4

9 + 5DT/16

ns

tDATTR

Data Disable After CLKIN4

0 – DT/8

7 – DT/8

ns

tACKEN

ACK Enable After CLKIN4

7.5 + DT/4

ns

tACKTR

ACK Disable After CLKIN4

–1 – DT/8

6 – DT/8

ns

tADCEN

ADRCLK Enable After CLKIN

–2 – DT/8

ns

tADCTR

ADRCLK Disable After CLKIN

8 – DT/4

ns

tMTRHBG

Memory Interface Disable Before HBG Low5

0 + DT/8

ns

tMENHBG

Memory Interface Enable After HBG High5

19 + DT

ns

1 For ADSP-21060L/ADSP-21060LC/ADSP-21062L, specification is –1.25 – DT/8 ns min, for ADSP-21062, specification is –1 – DT/8 ns min.

2 Strobes = RD, WR, PAGE, DMAG, BMS, SW.

3 For ADSP-21060LC, specification is 0.25 – DT/4 ns max.

4 In addition to bus master transition cycles, these specs also apply to bus master and bus slave synchronous read/write.

5 Memory Interface = Address, RD, WR, MSx, SW, PAGE, DMAGx, and BMS (in EPROM boot mode).

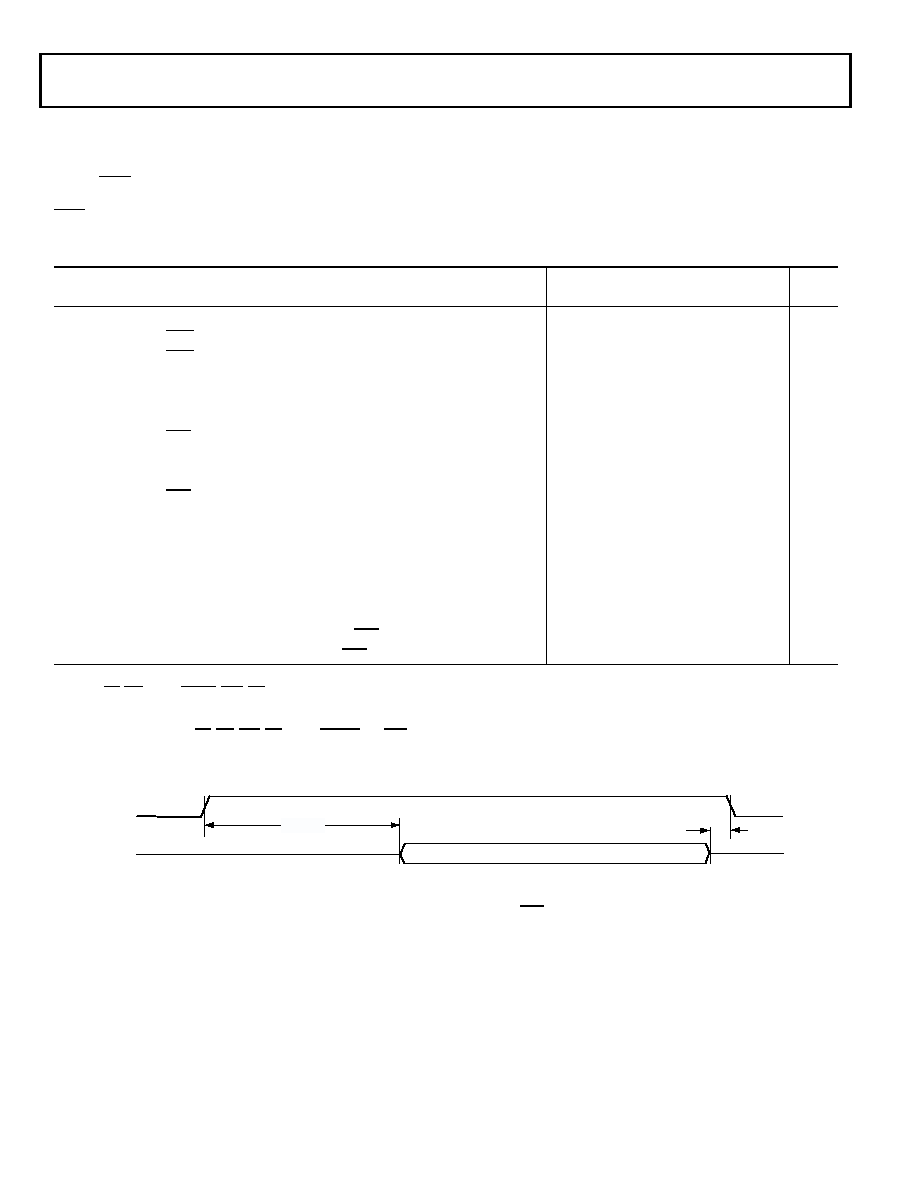

Figure 21. Three-State Timing (Bus Transition Cycle, SBTS Assertion)

MEMORY

INTERFACE

HBG

MEMORY INTERFACE = ADDRESS,

RD, WR, MSx, SW,PAGE, DMAGx. BMS (IN EPROM BOOT MODE)

tMENHBG

tMTRHBG

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B3K-CY-S | CONVERTER MOD DC/DC 40V 50W |

| ADSP-21060KS-133 | IC DSP CONTROLLER 32BIT 240MQFP |

| TPSW686M010R0100 | CAP TANT 68UF 10V 20% 2312 |

| VE-B3J-CY-S | CONVERTER MOD DC/DC 36V 50W |

| VI-B3Y-CY-F2 | CONVERTER MOD DC/DC 3.3V 33W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21060LKSZ-160 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21061 | 制造商:AD 制造商全称:Analog Devices 功能描述:ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21061KS | 制造商:Analog Devices 功能描述: |

| ADSP-21061KS-133 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21061KS-160 | 功能描述:IC DSP CONTROLLER 1MBIT 240MQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。