- 您现在的位置:买卖IC网 > PDF目录19377 > ADSP-21369BBP-2A (Analog Devices Inc)IC DSP 32BIT 333MHZ 256-BGA PDF资料下载

参数资料

| 型号: | ADSP-21369BBP-2A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 23/64页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 333MHZ 256-BGA |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI |

| 时钟速率: | 333MHz |

| 非易失内存: | ROM(768 kB) |

| 芯片上RAM: | 256kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA 裸露焊盘 |

| 供应商设备封装: | 256-BGA(27x27) |

| 包装: | 托盘 |

| 配用: | ADZS-21369-EZLITE-ND - KIT EVAL EZ LITE ADDS-21369 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Rev. F

|

Page 3 of 64

|

October 2013

GENERAL DESCRIPTION

The ADSP-21367/ADSP-21368/ADSP-21369 SHARC

proces-

sors are members of the SIMD SHARC family of DSPs that

feature Analog Devices’ Super Harvard Architecture. These pro-

cessors are source code-compatible with the ADSP-2126x and

ADSP-2116x DSPs as well as with first generation ADSP-2106x

SHARC processors in SISD (single-instruction, single-data)

mode. The processors are 32-bit/40-bit floating-point proces-

sors optimized for high performance automotive audio

applications with its large on-chip SRAM, mask programmable

ROM, multiple internal buses to eliminate I/O bottlenecks, and

an innovative digital applications interface (DAI).

As shown in the functional block diagram on Page 1, the

processors use two computational units to deliver a significant

performance increase over the previous SHARC processors on a

range of DSP algorithms. Fabricated in a state-of-the-art, high

speed, CMOS process, the ADSP-21367/ADSP-21368/

ADSP-21369 processors achieve an instruction cycle time of up

to 2.5 ns at 400 MHz. With its SIMD computational hardware,

the processors can perform 2.4 GFLOPS running at 400 MHz.

Table 1 shows performance benchmarks for these devices.

The diagram on Page 1 shows the two clock domains that make

up the ADSP-21367/ADSP-21368/ADSP-21369 processors. The

core clock domain contains the following features.

Two processing elements (PEx, PEy), each of which com-

prises an ALU, multiplier, shifter, and data register file

Data address generators (DAG1, DAG2)

Program sequencer with instruction cache

PM and DM buses capable of supporting 2x64-bit data

transfers between memory and the core at every core pro-

cessor cycle

One periodic interval timer with pinout

On-chip SRAM (2M bit)

On-chip mask-programmable ROM (6M bit)

JTAG test access port for emulation and boundary scan.

The JTAG provides software debug through user break-

points which allows flexible exception handling.

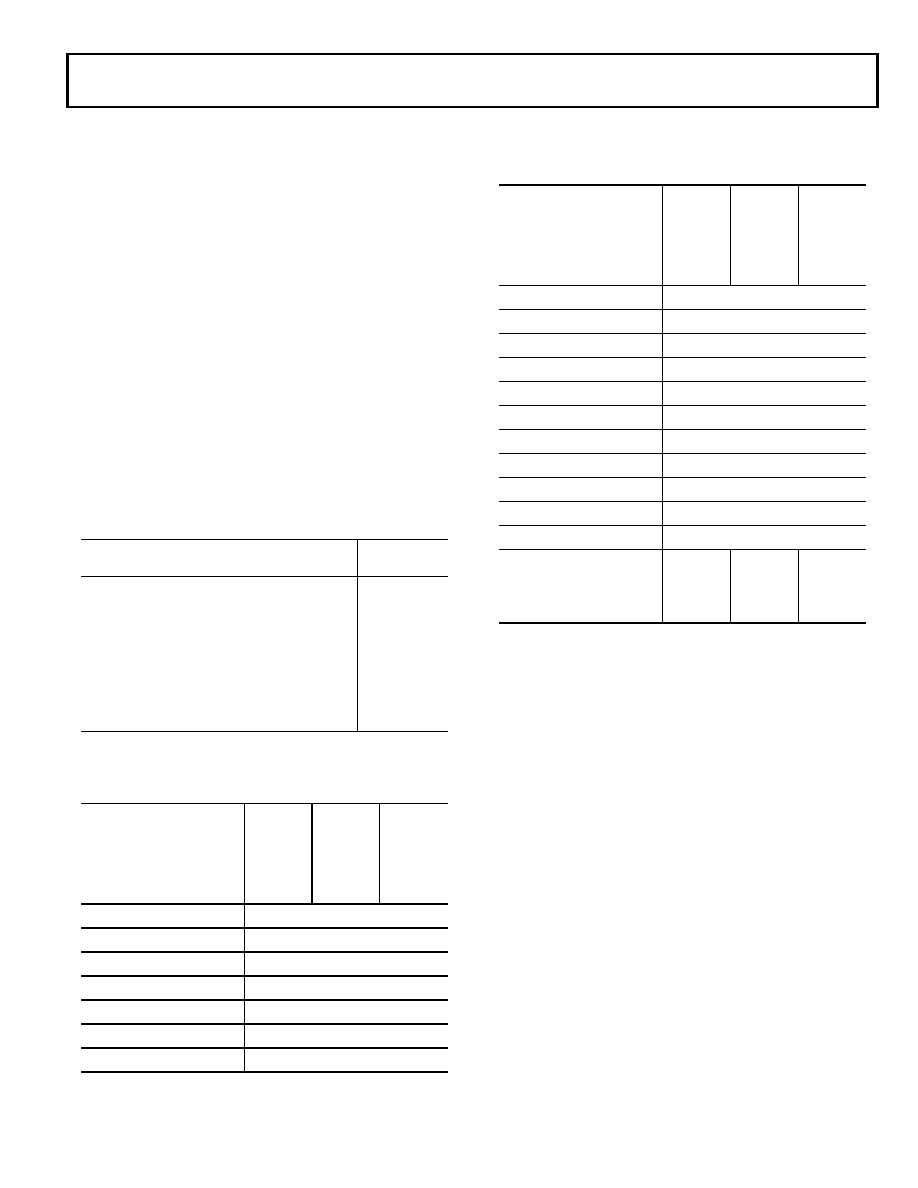

Table 1. Processor Benchmarks (at 400 MHz)

Benchmark Algorithm

Speed

(at 400 MHz)

1024 Point Complex FFT (Radix 4, with reversal) 23.2

s

FIR Filter (per tap)1

1 Assumes two files in multichannel SIMD mode.

1.25 ns

IIR Filter (per biquad)1

5.0 ns

Matrix Multiply (pipelined)

[3×3] × [3×1]

[4×4] × [4×1]

11.25 ns

20.0 ns

Divide (y/x)

8.75 ns

Inverse Square Root

13.5 ns

Table 2. ADSP-2136x Family Features1

Feature

ADSP

-2136

7

ADSP

-2136

8

ADSP

-2136

9/

ADSP

-2136

9W

Frequency

400 MHz

RAM

2M bits

ROM

2

6M bits

Audio Decoders in ROM

Yes

Pulse-Width Modulation

Yes

S/PDIF

Yes

SDRAM Memory Bus Width

32/16 bits

Serial Ports

8

IDP

Yes

DAI

Yes

UART

2

DAI

Yes

DPI

Yes

S/PDIF Transceiver

1

AMI Interface Bus Width

32/16/8 bits

SPI

2

TWI

Yes

SRC Performance

128 dB

Package

256 Ball-

BGA,

208-Lead

LQFP_EP

256 Ball-

BGA

256 Ball-

BGA,

208-Lead

LQFP_EP

1 W = Automotive grade product. See Automotive Products on Page 61 for more

information.

2 Audio decoding algorithms include PCM, Dolby Digital EX, Dolby Prologic IIx,

DTS 96/24, Neo:6, DTS ES, MPEG-2 AAC, MP3, and functions like bass

management, delay, speaker equalization, graphic equalization, and more.

Decoder/post-processor algorithm combination support varies depending upon

the chip version and the system configurations. Please visit www.analog.com for

complete information.

Table 2. ADSP-2136x Family Features1 (Continued)

Feature

ADSP

-2136

7

ADSP

-2136

8

ADSP

-2136

9/

ADSP

-2136

9W

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF561SBB600 | IC DSP 32BIT 600MHZ 297-BGA |

| RMC40DRXI | CONN EDGECARD 80POS DIP .100 SLD |

| GMM08DRSH-S288 | CONN EDGECARD 16POS .156 EXTEND |

| VE-B1M-CV-F3 | CONVERTER MOD DC/DC 10V 150W |

| TAJY157M010RNJ | CAP TANT 150UF 10V 20% 2917 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21369BBPZ-2A | 功能描述:IC DSP 32BIT 333MHZ 256-BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21369BSWZ-1A | 功能描述:IC DSP 32BIT 266MHZ 208LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21369BSWZ-2A | 功能描述:IC DSP 32BIT 333MHZ 208-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21369KBP-2A | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| ADSP-21369KBPZ-2A | 功能描述:IC DSP 32BIT 333MHZ 256-BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

发布紧急采购,3分钟左右您将得到回复。