- 您现在的位置:买卖IC网 > PDF目录19388 > ADSP-21489KSWZ-3A (Analog Devices Inc)IC CCD SIGNAL PROCESSOR 100LQFP PDF资料下载

参数资料

| 型号: | ADSP-21489KSWZ-3A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/68页 |

| 文件大小: | 0K |

| 描述: | IC CCD SIGNAL PROCESSOR 100LQFP |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | EBI/EMI,DAI,I²C,SPI,SPORT,UART/USART |

| 时钟速率: | 350MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 5Mb |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.10V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP 裸露焊盘 |

| 供应商设备封装: | 100-LQFP-EP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Rev. B

|

Page 22 of 68

|

March 2013

TIMING SPECIFICATIONS

Use the exact timing information given. Do not attempt to

derive parameters from the addition or subtraction of others.

While addition or subtraction would yield meaningful results

for an individual device, the values given in this data sheet

reflect statistical variations and worst cases. Consequently, it is

not meaningful to add parameters to derive longer times. See

Figure 43 on Page 55 for voltage reference levels.

Switching Characteristics specify how the processor changes its

signals. Circuitry external to the processor must be designed for

compatibility with these signal characteristics. Switching char-

acteristics describe what the processor will do in a given

circumstance. Use switching characteristics to ensure that any

timing requirement of a device connected to the processor (such

as memory) is satisfied.

Timing Requirements apply to signals that are controlled by cir-

cuitry external to the processor, such as the data input for a read

operation. Timing requirements guarantee that the processor

operates correctly with other devices.

Core Clock Requirements

The processor’s internal clock (a multiple of CLKIN) provides

the clock signal for timing internal memory, the processor core,

and the serial ports. During reset, program the ratio between the

processor’s internal clock frequency and external (CLKIN)

clock frequency with the CLK_CFG1–0 pins.

The processor’s internal clock switches at higher frequencies

than the system input clock (CLKIN). To generate the internal

clock, the processor uses an internal phase-locked loop (PLL,

see Figure 4). This PLL-based clocking minimizes the skew

between the system clock (CLKIN) signal and the processor’s

internal clock.

Voltage Controlled Oscillator (VCO)

In application designs, the PLL multiplier value should be

selected in such a way that the VCO frequency never exceeds

The product of CLKIN and PLLM must never exceed 1/2 of

(INDIV = 0).

The product of CLKIN and PLLM must never exceed fVCO

(max) in Table 20 if the input divider is enabled

(INDIV = 1).

The VCO frequency is calculated as follows:

fVCO = 2 × PLLM × fINPUT

fCCLK = (2 × PLLM × fINPUT) ÷ PLLD

where:

fVCO = VCO output

PLLM = Multiplier value programmed in the PMCTL register.

During reset, the PLLM value is derived from the ratio selected

using the CLK_CFG pins in hardware.

PLLD = 2, 4, 8, or 16 based on the divider value programmed on

the PMCTL register. During reset this value is 2.

fINPUT = is the input frequency to the PLL.

fINPUT = CLKIN when the input divider is disabled or

fINPUT = CLKIN ÷ 2 when the input divider is enabled

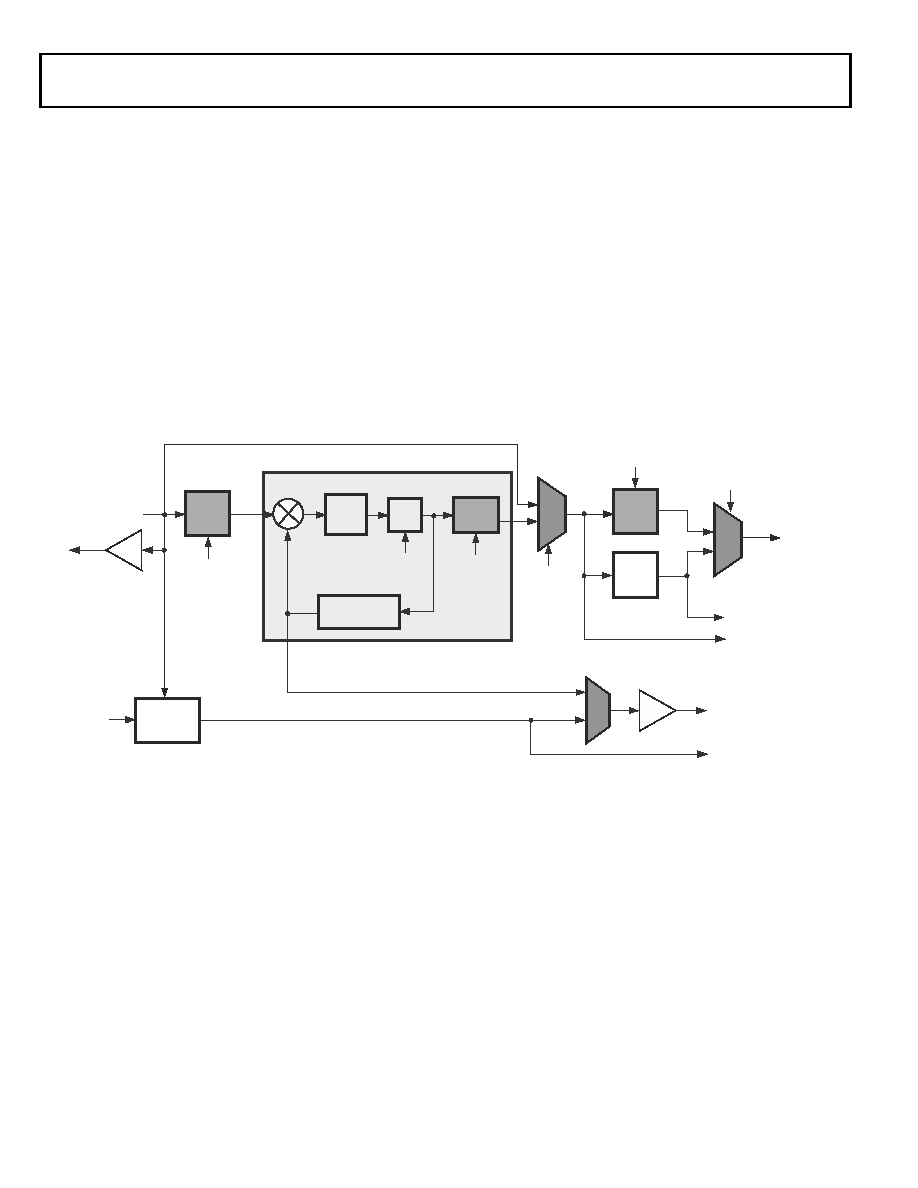

Figure 4. Core Clock and System Clock Relationship to CLKIN

LOOP

FILTER

CLKIN

PCLK

SDRAM

DIVIDER

BYPASS

MUX

PMCTL

(SDCKR)

CCLK

PLL

XTAL

CLKIN

DIVIDER

RESET

f

VCO ÷ (2 × PLLM)

BUF

VCO

BUF

PMCTL

(INDIV)

PLL

DIVIDER

RESETOUT

CLKOUT (TEST ONLY)*

DELAY OF

4096 CLKIN

CYCLES

PCLK

PMCTL

(PLLBP)

PMCTL

(PLLD)

f

VCO

f

CCLK

fINPUT

*CLKOUT (TEST ONLY) FREQUENCY IS THE SAME AS f

INPUT.

THIS SIGNAL IS NOT SPECIFIED OR SUPPORTED FOR ANY DESIGN.

CLK_CFGx/

PMCTL (2 × PLLM)

DIVIDE

BY 2

PIN

MUX

PMCTL

(PLLBP)

CCLK

RESETOUT

CORESRST

SDCLK

BYPASS

MUX

相关PDF资料 |

PDF描述 |

|---|---|

| MC7818CT | IC REG LDO 18V 1A TO220AB |

| TAJC477K002RNJ | CAP TANT 470UF 2.5V 10% 2312 |

| MC7815BT | IC REG LDO 15V 1A TO220AB |

| TPSW106M020R0500 | CAP TANT 10UF 20V 20% 2312 |

| MC7815ACT | IC REG LDO 15V 1A TO220AB |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21489KSWZ-3B | 功能描述:IC CCD SIGNAL PROCESSOR 176LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21489KSWZ-4A | 功能描述:IC CCD SIGNAL PROCESSOR 100LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21489KSWZ-4B | 功能描述:IC CCD SIGNAL PROCESSOR 176LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21489KSWZ-5B | 制造商:Analog Devices 功能描述:450 MHZ SHARC W/ STATIC VOLTAG 制造商:Analog Devices 功能描述:450 MHZ SHARC W/ STATIC VOLTAGE SCALING - Trays 制造商:Analog Devices 功能描述:Digital Signal Processors & Controllers - DSP, DSC High Perf 4th Generation 制造商:Analog Devices 功能描述:450 MHz SHARC w/ Static Voltage Scaling |

| ADSP-21489KSWZENGA | 制造商:Analog Devices 功能描述:SHARC PROCESSOR - Trays |

发布紧急采购,3分钟左右您将得到回复。