- 您现在的位置:买卖IC网 > PDF目录19473 > ADSP-2187NBSTZ-320 (Analog Devices Inc)IC DSP CONTROLLER 16BIT 100LQFP PDF资料下载

参数资料

| 型号: | ADSP-2187NBSTZ-320 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 45/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 16BIT 100LQFP |

| 标准包装: | 1 |

| 系列: | ADSP-21xx |

| 类型: | 定点 |

| 接口: | 主机接口,串行端口 |

| 时钟速率: | 80MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 160kB |

| 电压 - 输入/输出: | 1.8V,2.5V,3.3V |

| 电压 - 核心: | 1.90V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页当前第45页第46页第47页第48页

Rev. A

|

Page 6 of 48

|

August 2006

ADSP-218xN

Interrupt routines can either be nested with higher priority

interrupts taking precedence or processed sequentially. Inter-

rupts can be masked or unmasked with the IMASK register.

Individual interrupt requests are logically ANDed with the bits

in IMASK; the highest priority unmasked interrupt is then

selected. The power-down interrupt is nonmaskable.

ADSP-218xN series members mask all interrupts for one

instruction cycle following the execution of an instruction that

modifies the IMASK register. This does not affect serial port

autobuffering or DMA transfers.

The interrupt control register, ICNTL, controls interrupt nest-

ing and defines the IRQ0, IRQ1, and IRQ2 external interrupts to

be either edge- or level-sensitive. The IRQE pin is an external

edge-sensitive interrupt and can be forced and cleared. The

IRQL0 and IRQL1 pins are external level sensitive interrupts.

The IFC register is a write-only register used to force and clear

interrupts. On-chip stacks preserve the processor status and are

automatically maintained during interrupt handling. The stacks

are 12 levels deep to allow interrupt, loop, and subroutine nest-

ing. The following instructions allow global enable or disable

servicing of the interrupts (including power-down), regardless

of the state of IMASK:

ENA INTS;

DIS INTS;

Disabling the interrupts does not affect serial port autobuffering

or DMA. When the processor is reset, interrupt servicing

is enabled.

LOW-POWER OPERATION

ADSP-218xN series members have three low-power modes that

significantly reduce the power dissipation when the device oper-

ates under standby conditions. These modes are:

Power-Down

Idle

Slow Idle

The CLKOUT pin may also be disabled to reduce external

power dissipation.

Power-Down

ADSP-218xN series members have a low-power feature that lets

the processor enter a very low-power dormant state through

hardware or software control. Following is a brief list of power-

down features. Refer to the ADSP-218x DSP Hardware Refer-

ence, “System Interface” chapter, for detailed information about

the power-down feature.

Quick recovery from power-down. The processor begins

executing instructions in as few as 200 CLKIN cycles.

Support for an externally generated TTL or CMOS proces-

sor clock. The external clock can continue running during

power-down without affecting the lowest power rating and

200 CLKIN cycle recovery.

Support for crystal operation includes disabling the oscilla-

tor to save power (the processor automatically waits

approximately 4096 CLKIN cycles for the crystal oscillator

to start or stabilize), and letting the oscillator run to allow

200 CLKIN cycle start-up.

Power-down is initiated by either the power-down pin

(PWD) or the software power-down force bit. Interrupt

support allows an unlimited number of instructions to be

executed before optionally powering down. The power-

down interrupt also can be used as a nonmaskable, edge-

sensitive interrupt.

Context clear/save control allows the processor to continue

where it left off or start with a clean context when leaving

the power-down state.

The RESET pin also can be used to terminate power-down.

Power-down acknowledge pin (PWDACK) indicates when

the processor has entered power-down.

Idle

When the ADSP-218xN is in the Idle Mode, the processor waits

indefinitely in a low-power state until an interrupt occurs.

When an unmasked interrupt occurs, it is serviced; execution

then continues with the instruction following the IDLE instruc-

tion. In Idle mode IDMA, BDMA, and autobuffer cycle steals

still occur.

Slow Idle

The IDLE instruction is enhanced on ADSP-218xN series mem-

bers to let the processor’s internal clock signal be slowed, further

reducing power consumption. The reduced clock frequency, a

programmable fraction of the normal clock rate, is specified by a

selectable divisor given in the IDLE instruction.

The format of the instruction is:

IDLE (n);

where n = 16, 32, 64, or 128. This instruction keeps the proces-

sor fully functional, but operating at the slower clock rate. While

it is in this state, the processor’s other internal clock signals,

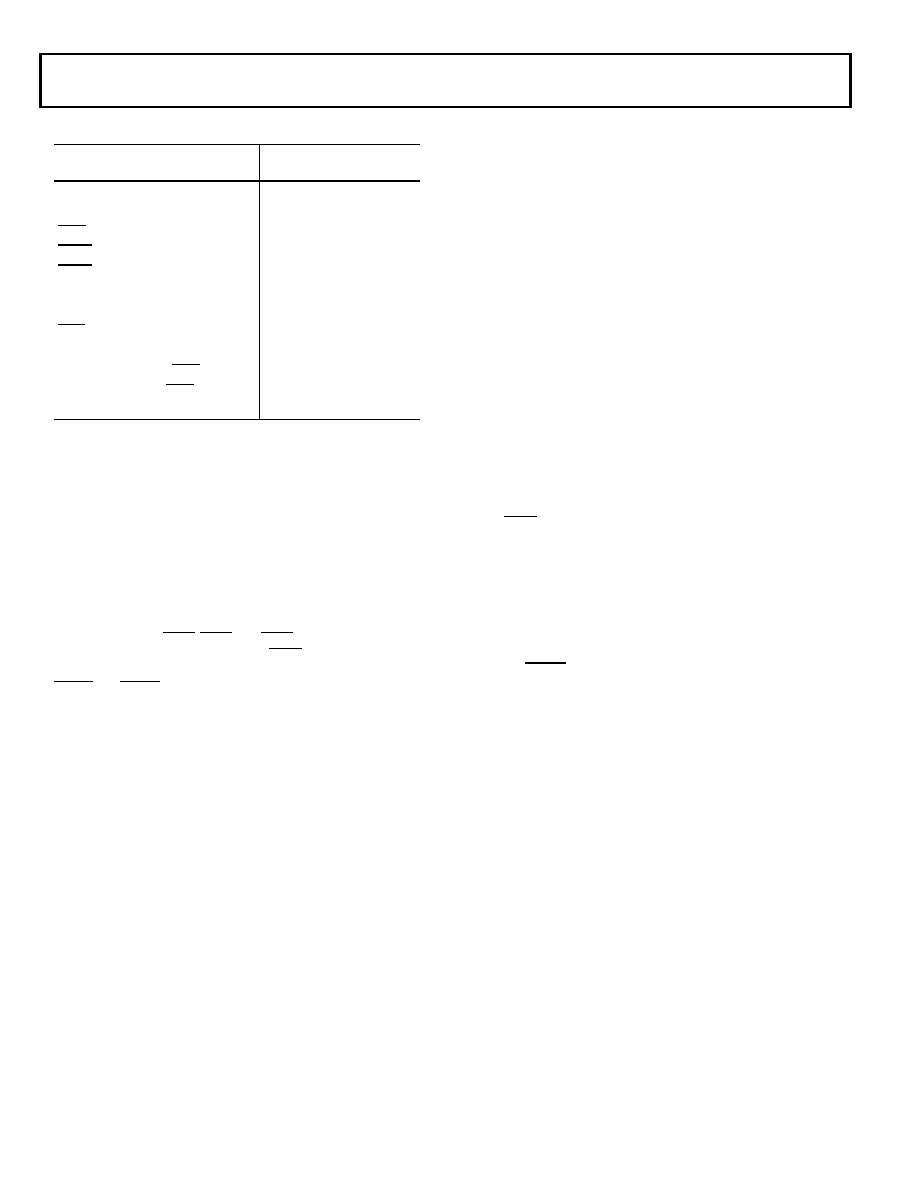

Table 3. Interrupt Priority and Interrupt Vector Addresses

Source Of Interrupt

Interrupt Vector Address

(Hex)

Reset (or Power-Up with PUCR = 1) 0x0000 (Highest Priority)

Power-Down (Nonmaskable)

0x002C

IRQ2

0x0004

IRQL1

0x0008

IRQL0

0x000C

SPORT0 Transmit

0x0010

SPORT0 Receive

0x0014

IRQE

0x0018

BDMA Interrupt

0x001C

SPORT1 Transmit or IRQ1

0x0020

SPORT1 Receive or IRQ0

0x0024

Timer

0x0028 (Lowest Priority)

相关PDF资料 |

PDF描述 |

|---|---|

| ACM28DTBS | CONN EDGECARD 56POS R/A .156 SLD |

| ADSP-2187NKSTZ-320 | IC DSP CONTROLLER 16BIT 100LQFP |

| ECC22DJWN-S1136 | CONN EDGECARD 44PS .100 PRESSFIT |

| NML1212SC | CONV DC/DC 2W 12VIN 12VOUT SIP |

| VI-B1V-CX-B1 | CONVERTER MOD DC/DC 5.8V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-2187NBSTZ-3202 | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-2187NKCA-320 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 80MHz 80MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:32K PM/32K DM RAM,16-BIT,80 MIPS, 1.8V - Bulk |

| ADSP-2187NKST-320 | 制造商:Rochester Electronics LLC 功能描述:32K PM/32K DM RAM,16-BIT, 80 MIPS, 1.8V - Bulk 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

| ADSP-2187NKSTZ-320 | 功能描述:IC DSP CONTROLLER 16BIT 100LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:ADSP-21xx 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-2187NKSTZ-3202 | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer |

发布紧急采购,3分钟左右您将得到回复。