- 您现在的位置:买卖IC网 > PDF目录223311 > ADSP-2189NBSTZ-320 (ANALOG DEVICES INC) 16-Bit, 80MIPS, 1.8V, 2 Serial Ports, Host Port, 192KB RAM; Package: 100 ld LQFP; No of Pins: 100; Temperature Range: Ind PDF资料下载

参数资料

| 型号: | ADSP-2189NBSTZ-320 |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 16-Bit, 80MIPS, 1.8V, 2 Serial Ports, Host Port, 192KB RAM; Package: 100 ld LQFP; No of Pins: 100; Temperature Range: Ind |

| 中文描述: | 24-BIT, 40 MHz, OTHER DSP, PQFP100 |

| 封装: | LEAD FREE, MS-026BED, LQFP-100 |

| 文件页数: | 5/48页 |

| 文件大小: | 2334K |

| 代理商: | ADSP-2189NBSTZ-320 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

ADSP-218xN

Rev. A

|

Page 13 of 48

|

August 2006

The BDMA circuit supports four different data formats that are

selected by the BTYPE register field. The appropriate number of

8-bit accesses are done from the byte memory space to build the

word size selected. Table 7 shows the data formats supported by

the BDMA circuit.

Unused bits in the 8-bit data memory formats are filled with 0s.

The BIAD register field is used to specify the starting address for

the on-chip memory involved with the transfer. The 14-bit

BEAD register specifies the starting address for the external byte

memory space. The 8-bit BMPAGE register specifies the start-

ing page for the external byte memory space. The BDIR register

field selects the direction of the transfer. Finally, the 14-bit

BWCOUNT register specifies the number of DSP words to

transfer and initiates the BDMA circuit transfers.

BDMA accesses can cross page boundaries during sequential

addressing. A BDMA interrupt is generated on the completion

of the number of transfers specified by the BWCOUNT register.

The BWCOUNT register is updated after each transfer so it can

be used to check the status of the transfers. When it reaches

zero, the transfers have finished and a BDMA interrupt is gener-

ated. The BMPAGE and BEAD registers must not be accessed

by the DSP during BDMA operations.

The source or destination of a BDMA transfer will always be on-

chip program or data memory.

When the BWCOUNT register is written with a nonzero value

the BDMA circuit starts executing byte memory accesses with

wait states set by BMWAIT. These accesses continue until the

count reaches zero. When enough accesses have occurred to

create a destination word, it is transferred to or from on-chip

memory. The transfer takes one DSP cycle. DSP accesses to

external memory have priority over BDMA byte mem-

ory accesses.

The BDMA Context Reset bit (BCR) controls whether the pro-

cessor is held off while the BDMA accesses are occurring.

Setting the BCR bit to 0 allows the processor to continue opera-

tions. Setting the BCR bit to 1 causes the processor to stop

execution while the BDMA accesses are occurring, to clear the

context of the processor, and start execution at address 0 when

the BDMA accesses have completed.

The BDMA overlay bits specify the OVLAY memory blocks to

be accessed for internal memory. Set these bits as indicated in

Note

: BDMA cannot access external overlay memory regions 1

and 2.

The BMWAIT field, which has four bits on ADSP-218xN series

members, allows selection up to 15 wait states for BDMA

transfers.

Internal Memory DMA Port (IDMA Port; Host Memory

Mode)

The IDMA Port provides an efficient means of communication

between a host system and ADSP-218xN series members. The

port is used to access the on-chip program memory and data

memory of the DSP with only one DSP cycle per word over-

head. The IDMA port cannot, however, be used to write to the

DSP’s memory-mapped control registers. A typical IDMA

transfer process is shown as follows:

1. Host starts IDMA transfer.

2. Host checks IACK control line to see if the DSP is busy.

3. Host uses IS and IAL control lines to latch either the DMA

starting address (IDMAA) or the PM/DM OVLAY selec-

tion into the DSP’s IDMA control registers. If Bit 15 = 1,

the values of Bits 7–0 represent the IDMA overlay; Bits

14–8 must be set to 0. If Bit 15 = 0, the value of Bits 13–0

represent the starting address of internal memory to be

accessed and Bit 14 reflects PM or DM for access. Set

IDDMOVLAY and IDPMOVLAY bits in the IDMA over-

lay register as indicted in Table 8.

4. Host uses IS and IRD (or IWR) to read (or write) DSP

internal memory (PM or DM).

5. Host checks IACK line to see if the DSP has completed the

previous IDMA operation.

6. Host ends IDMA transfer.

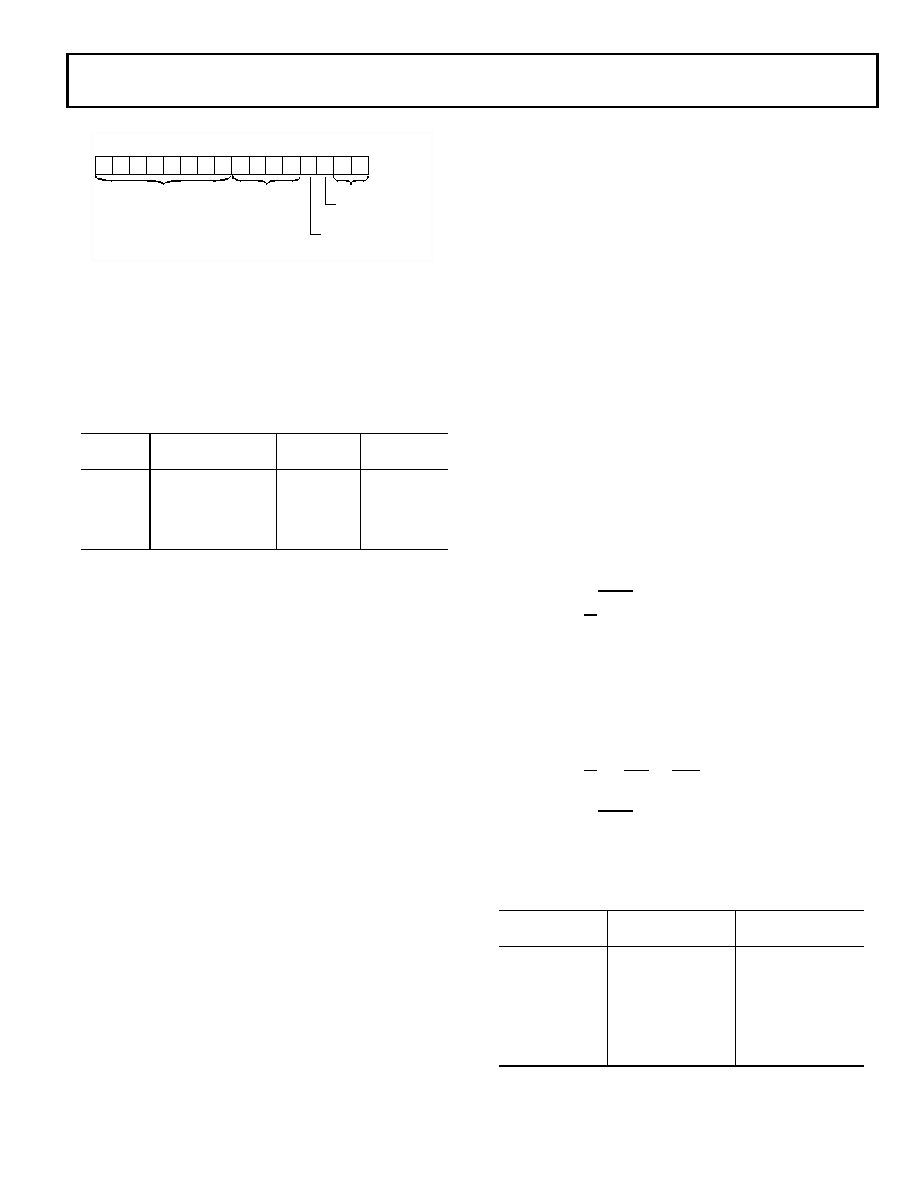

Figure 13. BDMA Control Register

Table 7. Data Formats

BTYPE

Internal Memory

Space

Word Size

Alignment

00

Program Memory

24

Full Word

01

Data Memory

16

Full Word

10

Data Memory

8

MSBs

11

Data Memory

8

LSBs

BDMA CONTROL

BMPAGE

BTYPE

BDIR

0= LOAD FROM BM

1= STORE TO BM

BCR

0 = RUN DURING BDMA

1 = HALT DURING BDMA

0

00

000

0

100

0

15 14 13 12 11 10

98

765

4

3

2

1

0

DM (0x3FE3)

BDMA

OVERLAY

BITS

(SEE TABLE 12)

Table 8. IDMA/BDMA Overlay Bits

Processor

IDMA/BDMA

PMOVLAY

IDMA/BDMA

DMOVLAY

ADSP-2184N

0

ADSP-2185N

0

ADSP-2186N

0

ADSP-2187N

0, 4, 5

ADSP-2188N

0, 4, 5, 6, 7

0, 4, 5, 6, 7, 8

ADSP-2189N

0, 4, 5

0, 4, 5, 6, 7

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-2189NKCAZ-320 | 16-Bit, 80MIPS, 1.8V, 2 Serial Ports, Host Port, 192KB RAM; Package: CHIP SCALE BGA; No of Pins: 144; Temperature Range: Comm. |

| ADSP-2189NKSTZ-320 | 16-Bit, 80MIPS, 1.8V, 2 Serial Ports, Host Port, 192KB RAM; Package: 100 ld LQFP; No of Pins: 100; Temperature Range: Comm. |

| ADSP-2191MBCAZ-140 | 16-bit Fixed-Point DSP, 160 MIPS, 160K bytes RAM; Package: CHIP SCALE BGA; No of Pins: 144; Temperature Range: Ind |

| ADSP-2191MBSTZ-140 | 16-bit Fixed-Point DSP, 160 MIPS, 160K bytes RAM; Package: 144 ld LQFP (20x20mm); No of Pins: 144; Temperature Range: Ind |

| ADSP-2191MKCAZ-160 | 16-bit Fixed-Point DSP, 160 MIPS, 160K bytes RAM; Package: CHIP SCALE BGA; No of Pins: 144; Temperature Range: Comm. |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-2189NBSTZ-3202 | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-2189NKCA-320 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 80MHz 80MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:32K PM/48K DM RAM,16-BIT,80 MIPS, 1.8V - Bulk |

| ADSP-2189NKCAZ-320 | 功能描述:IC DSP 16BIT 80MHZ 144CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:ADSP-21xx 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-2189NKCAZ-3202 | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-2189NKST-320 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 80MHz 80MIPS 100-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:32K PM/48K DM RAM,16-BIT, 80 MIPS, 1.8V - Bulk 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

发布紧急采购,3分钟左右您将得到回复。