- 您现在的位置:买卖IC网 > PDF目录19394 > ADSP-BF526KBCZ-3C2 (Analog Devices Inc)IC DSP CTRLR 300MHZ 289CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF526KBCZ-3C2 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/36页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTRLR 300MHZ 289CSPBGA |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | DMA,以太网,I²C,PPI,SPI,SPORT,UART,USB |

| 时钟速率: | 300MHz |

| 非易失内存: | ROM(32 kB) |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 1.8V,2.5V,3.3V |

| 电压 - 核心: | 1.30V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 289-LFBGA,CSPBGA |

| 供应商设备封装: | 289-CSPBGA(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Rev. A

|

Page 20 of 36

|

March 2010

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

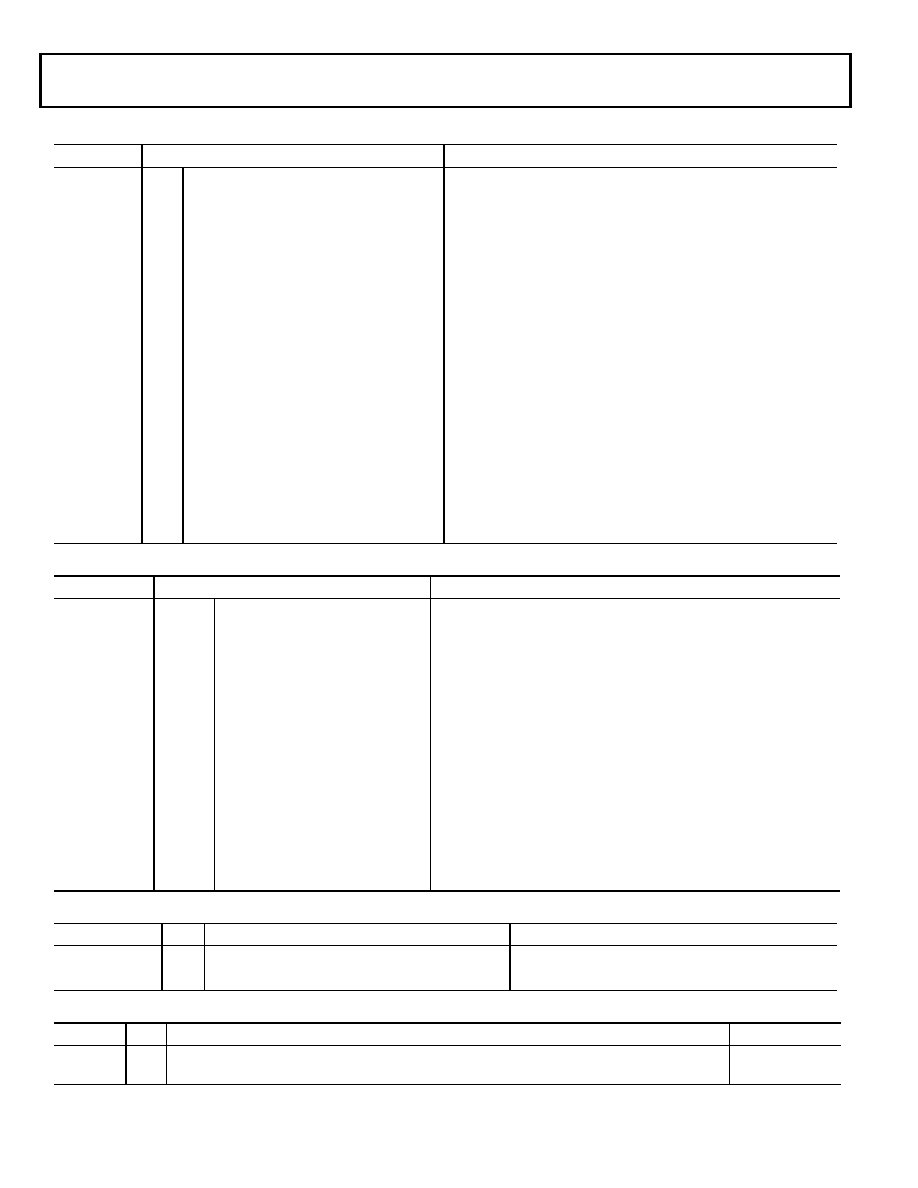

Table 11. Register 7 Digital Audio I/F

Bit Name

Bits

Description

Settings

BCLKINV

B7

CODEC_BCLK inversion control

0 = CODEC_BCLK not inverted (default)

1 = CODEC_BCLK inverted

MS

B6

Master mode enable

0 = enable slave mode (default)

1 = enable master mode

LRSWAP

B5

Swap DAC data control

0 = output left- and right-channel data as normal (default)

1 = swap left- and right-channel DAC data in audio interface

LRP

B4

Polarity control for clocks in right-justified,

left-justified, and I2S modes

0 = normal DACLRC and ADCLRC (default),

or processor Submode 1

1 = invert DACLRC and ADCLRC polarity, or processor Submode 2

WL [1:0]

B[3:2] Data-word length control

00 = 16 bits

01 = 20 bits

10 = 24 bits (default)

11 = 32 bits

FORMAT [1:0]

B[1:0] Digital audio input format control

00 = right justified

01 = left justified

10 = I2S mode (default)

11 = processor mode

Table 12. Register 8 Sampling Rate

Bit Name

Bits

Description

Settings

CLKODIV2

B7

CODEC_CLKOUT divider select

0 = CODEC_CLKOUT is codec clock (default)

1 = CODEC_CLKOUT is codec clock divided by 2

CLKDIV2

B6

Codec clock divide select

0 = codec clock is CODEC_MCLK (default)

1= codec clock is CODEC_MCLK divided by 2

SR [3:0]

B[5:2]

Clock setting condition

See Table 1 on Page 9 and Table 2 on Page 10

BOSR

B1

Base oversampling rate

USB mode:

0 = support for 250 × fS based clock (default)

1 = support for 272 × fS based clock

Normal mode:

0 = support for 256 × fS based clock (default)

1 = support for 384 × fS based clock

USB

B0

USB mode select

0 = normal mode enable (default)

1 = USB mode enable

Table 13. Register 9 Active

Bit Name

Bit

Description

Settings

ACTIVE

B0

Digital core activation control

0 = disable digital core (default)

1 = activate digital core

Table 14. Register 10 Software Reset

Bit Name

Bit

Description

Settings

RESET [8:0] B[8:0] Write all 0s to this register to set all registers to their default settings.

Other data written to this register has no effect.

0 = reset (default)

相关PDF资料 |

PDF描述 |

|---|---|

| TAP156M025BRW | CAP TANT 15UF 25V 20% RADIAL |

| RSA40DRMD-S288 | CONN EDGECARD 80POS .125 EXTEND |

| ADSP21262SKBCZ200R | IC DSP CTLR 32BIT 136CSPBGA |

| MAX6505UTP080+T | IC TEMP SWITCH DL TRIP SOT23-6 |

| RW2-2405D/H3/B | CONV DC/DC 2W 18-36VIN +/-05VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF526KBCZ-4 | 功能描述:IC DSP CTRLR 400MHZ 289CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF526KBCZ-4C2 | 功能描述:IC DSP CTRLR 400MHZ 289CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF526KBCZ4C2X | 制造商:Analog Devices 功能描述:DSP 32-BIT 400MHZ - Trays |

| ADSP-BF526KBCZ-4X | 制造商:Analog Devices 功能描述:LOW POWER BLACKFIN PROCESSOR WITH ADVANCED PERIPHERALS AND L - Trays |

| ADSP-BF526KBCZENGA | 制造商:Analog Devices 功能描述:LOW POWER BLACKFIN PROCESSOR WITH ADVANCED PERIPHERALS AND L - Trays |

发布紧急采购,3分钟左右您将得到回复。