- 您现在的位置:买卖IC网 > PDF目录19382 > ADSP-BF561SKBCZ-5V (Analog Devices Inc)IC DSP 32BIT 500MHZ 256CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF561SKBCZ-5V |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/64页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 500MHZ 256CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | SPI,SSP,UART |

| 时钟速率: | 533MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 328kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.25V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LFBGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BF561-EZLITE-ND - BOARD EVAL ADSP-BF561 ADZS-BF561-MMSKIT-ND - KIT STARTER MULTIMEDIA BF561 ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

�� �

�

�

�ADSP-BF561 �

�writing� the� appropriate� values� into� the� Interrupt� Assignment�

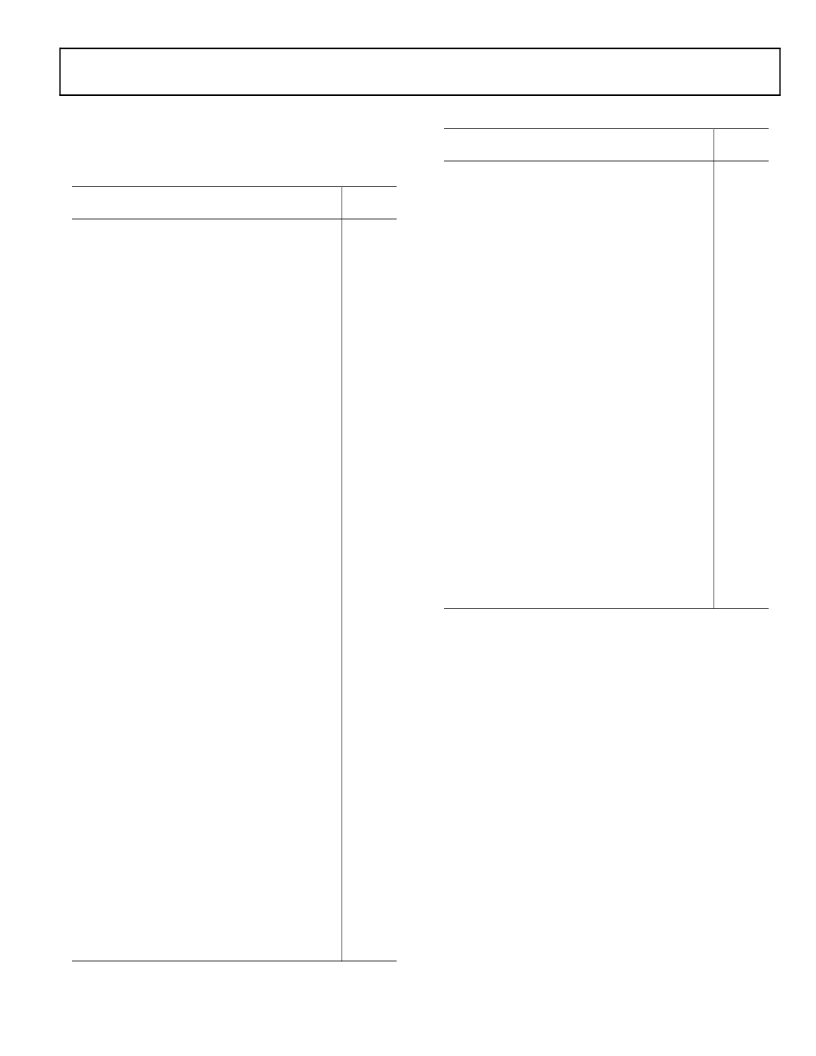

�Table� 2.� System� Interrupt� Controller� (SIC)� (Continued)�

�Registers� (SIC_IAR7–0).� Table� 2� describes� the� inputs� into� the�

�SIC� and� the� default� mappings� into� the� CEC.�

�Table� 2.� System� Interrupt� Controller� (SIC)�

�Peripheral� Interrupt� Event�

�Timer7� Interrupt�

�Default� �

�Mapping �

�IVG10�

�Peripheral� Interrupt� Event�

�PLL� Wakeup�

�DMA1� Error� (Generic)�

�DMA2� Error� (Generic)�

�IMDMA� Error�

�PPI0� Error�

�PPI1� Error�

�SPORT0� Error�

�SPORT1� Error�

�SPI� Error�

�UART� Error�

�Reserved�

�DMA1� Channel� 0� Interrupt� (PPI0)�

�DMA1� Channel� 1� Interrupt� (PPI1)�

�DMA1� Channel� 2� Interrupt�

�DMA1� Channel� 3� Interrupt�

�DMA1� Channel� 4� Interrupt�

�DMA1� Channel� 5� Interrupt�

�DMA1� Channel� 6� Interrupt�

�DMA1� Channel� 7� Interrupt�

�DMA1� Channel� 8� Interrupt�

�DMA1� Channel� 9� Interrupt�

�DMA1� Channel� 10� Interrupt�

�DMA1� Channel� 11� Interrupt�

�Default� �

�Mapping �

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

�IVG8�

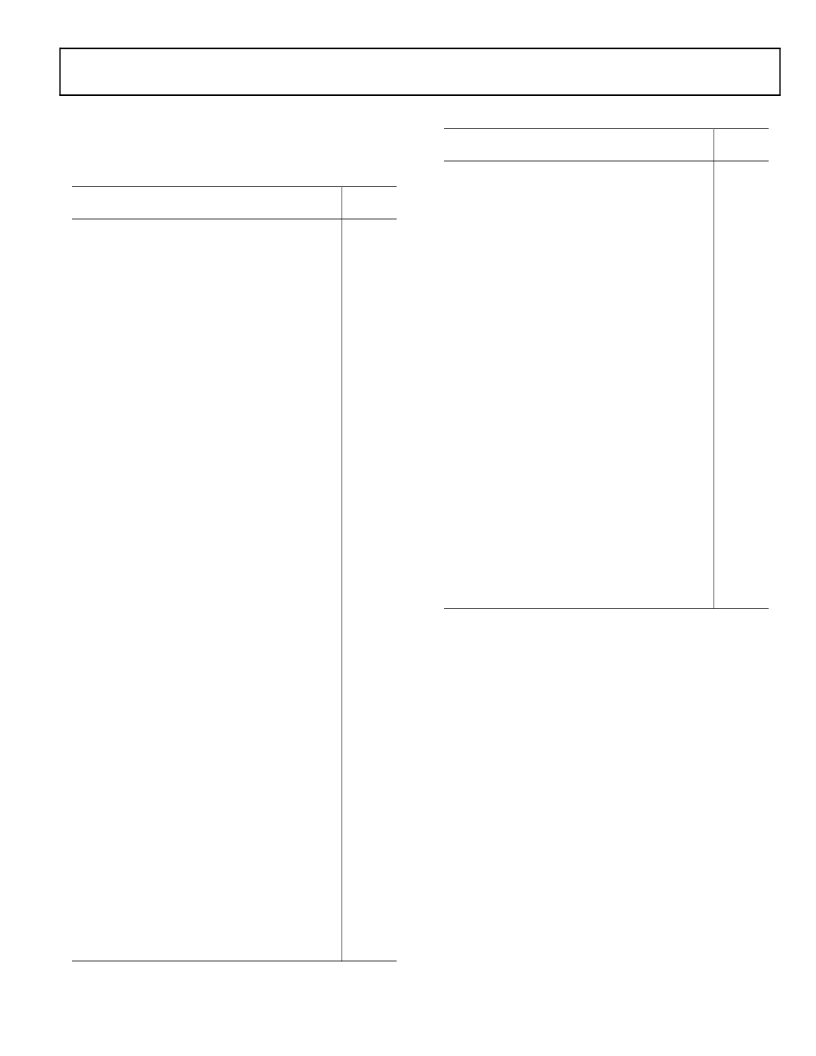

�Timer8� Interrupt�

�Timer9� Interrupt�

�Timer10� Interrupt�

�Timer11� Interrupt�

�Programmable� Flags� 15–0� Interrupt� A�

�Programmable� Flags� 15–0� Interrupt� B�

�Programmable� Flags� 31–16� Interrupt� A�

�Programmable� Flags� 31–16� Interrupt� B�

�Programmable� Flags� 47–32� Interrupt� A�

�Programmable� Flags� 47–32� Interrupt� B�

�DMA1� Channel� 12/13� Interrupt�

�(Memory� DMA/Stream� 0)�

�DMA1� Channel� 14/15� Interrupt�

�(Memory� DMA/Stream� 1)�

�DMA2� Channel� 12/13� Interrupt�

�(Memory� DMA/Stream� 0)�

�DMA2� Channel� 14/15� Interrupt�

�(Memory� DMA/Stream� 1)�

�IMDMA� Stream� 0� Interrupt�

�IMDMA� Stream� 1� Interrupt�

�Watchdog� Timer� Interrupt�

�Reserved�

�Reserved�

�Supplemental� Interrupt� 0�

�Supplemental� Interrupt� 1�

�IVG10�

�IVG10�

�IVG10�

�IVG10�

�IVG11�

�IVG11�

�IVG11�

�IVG11�

�IVG11�

�IVG11�

�IVG8�

�IVG8�

�IVG9�

�IVG9�

�IVG12�

�IVG12�

�IVG13�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�DMA2� Channel� 0� Interrupt� (SPORT0� Rx)�

�DMA2� Channel� 1� Interrupt� (SPORT0� Tx)�

�DMA2� Channel� 2� Interrupt� (SPORT1� Rx)�

�DMA2� Channel� 3� Interrupt� (SPORT1� Tx)�

�DMA2� Channel� 4� Interrupt� (SPI)�

�DMA2� Channel� 5� Interrupt� (UART� Rx)�

�DMA2� Channel� 6� Interrupt� (UART� Tx)�

�DMA2� Channel� 7� Interrupt�

�DMA2� Channel� 8� Interrupt�

�DMA2� Channel� 9� Interrupt�

�DMA2� Channel� 10� Interrupt�

�DMA2� Channel� 11� Interrupt�

�Timer0� Interrupt�

�Timer1� Interrupt�

�Timer2� Interrupt�

�Timer3� Interrupt�

�Timer4� Interrupt�

�Timer5� Interrupt�

�Timer6� Interrupt�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG10�

�IVG10�

�IVG10�

�IVG10�

�IVG10�

�IVG10�

�IVG10�

�Event� Control�

�The� ADSP-BF561� provides� the� user� with� a� very� flexible� mecha-�

�nism� to� control� the� processing� of� events.� In� the� CEC,� three�

�registers� are� used� to� coordinate� and� control� events.� Each� of� the�

�registers� is� 16� bits� wide,� while� each� bit� represents� a� particular�

�event� class.�

�?� CEC� Interrupt� Latch� Register� (ILAT)� –� The� ILAT� register�

�indicates� when� events� have� been� latched.� The� appropriate�

�bit� is� set� when� the� processor� has� latched� the� event� and�

�cleared� when� the� event� has� been� accepted� into� the� system.�

�This� register� is� updated� automatically� by� the� controller,� but�

�may� also� be� written� to� clear� (cancel)� latched� events.� This�

�register� may� be� read� while� in� supervisor� mode� and� may�

�only� be� written� while� in� supervisor� mode� when� the� corre-�

�sponding� IMASK� bit� is� cleared.�

�?� CEC� Interrupt� Mask� Register� (IMASK)� –� The� IMASK� reg-�

�ister� controls� the� masking� and� unmasking� of� individual�

�events.� When� a� bit� is� set� in� the� IMASK� register,� that� event� is�

�unmasked� and� will� be� processed� by� the� CEC� when� asserted.�

�A� cleared� bit� in� the� IMASK� register� masks� the� event,�

�thereby� preventing� the� processor� from� servicing� the� event�

�Rev.� E� |�

�Page� 7� of� 64� |�

�September� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| VI-B23-CY-F4 | CONVERTER MOD DC/DC 24V 50W |

| 56F011-104 | CONN FILTER MICRO-D 15P 1500PF |

| TAP475J050SCS | CAP TANT 4.7UF 50V 5% RADIAL |

| 56F011-114 | CONN FILTER MICRO-D 15P 4700PF |

| 56F001-104 | CONN FILTER MICRO-D 9P 1500PF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF561SKBCZ600 | 制造商:Analog Devices 功能描述:DSP FIX PT 16BIT 600MHZ 600MIPS 256CSPBGA - Trays 制造商:Analog Devices 功能描述:IC MULTI-PROCESSOR |

| ADSP-BF561SKBCZ-6A | 功能描述:IC DSP CTRLR 32B 600MHZ 256CPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF561SKBCZ-6A | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

| ADSP-BF561SKBCZ-6V | 功能描述:IC DSP 32BIT 600MHZ 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF561SKBCZC70 | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。