- 您现在的位置:买卖IC网 > PDF目录10937 > ADV202BBCZ-115 (Analog Devices Inc)IC VIDEO CODEC JPEG2000 121-BGA PDF资料下载

参数资料

| 型号: | ADV202BBCZ-115 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 25/40页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO CODEC JPEG2000 121-BGA |

| 标准包装: | 1 |

| 类型: | JPEG2000 视频编解码器 |

| 分辨率(位): | 16 b |

| 三角积分调变: | 无 |

| 电压 - 电源,模拟: | 1.5V,3.3V |

| 电压 - 电源,数字: | 1.5V,3.3V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 121-BGA,CSPBGA |

| 供应商设备封装: | 121-CSPBGA(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

Data Sheet

ADV202

Rev. D | Page 31 of 40

PLL

The ADV202 uses the PLL_HI and PLL_LO direct registers to

configure the PLL. Any time the PLL_LO register is modified,

the host must wait at least 20 s before reading or writing to any

other register. If this delay is not implemented, erratic behavior

could result.

The PLL can be programmed to have any possible final

multiplier value as long as

JCLK > 50 MHz and < 150 MHz (144-lead version).

JCLK > 50 MHz and < 135 MHz (144-lead version).

JCLK > 50 MHz and < 115 MHz (121-lead version).

HCLK < 108 MHz (144-lead, 150 MHz version).

HCLK < 100 MHz (144-lead, 135 MHz version).

HCLK < 81 MHz (121-lead version).

JCLK ≥ 2 × VCLK for single-component input.

JCLK ≥ 2 × VCLK for YCrCb [4:2:2] input.

In JDATA mode (JDATA), JCLK must be 4 × MCLK or

higher.

For de-interlaced modes, JCLK must be ≥ 4 × MCLK.

The maximum burst frequency for external DMA modes is

≤0.36 JCLK.

For MCLK frequencies greater than 50 MHz, the input

clock divider must be enabled, that is, IPD set to 1.

IPD cannot be enabled for MCLK frequencies below 20 MHz.

To achieve the lowest power consumption, an MCLK frequency

of 27 MHz is recommended for a standard definition CCIR656

input. The PLL circuit is recommended to have a multiplier of 3.

This sets JCLK and HCLK to 81 MHz.

04723-

009

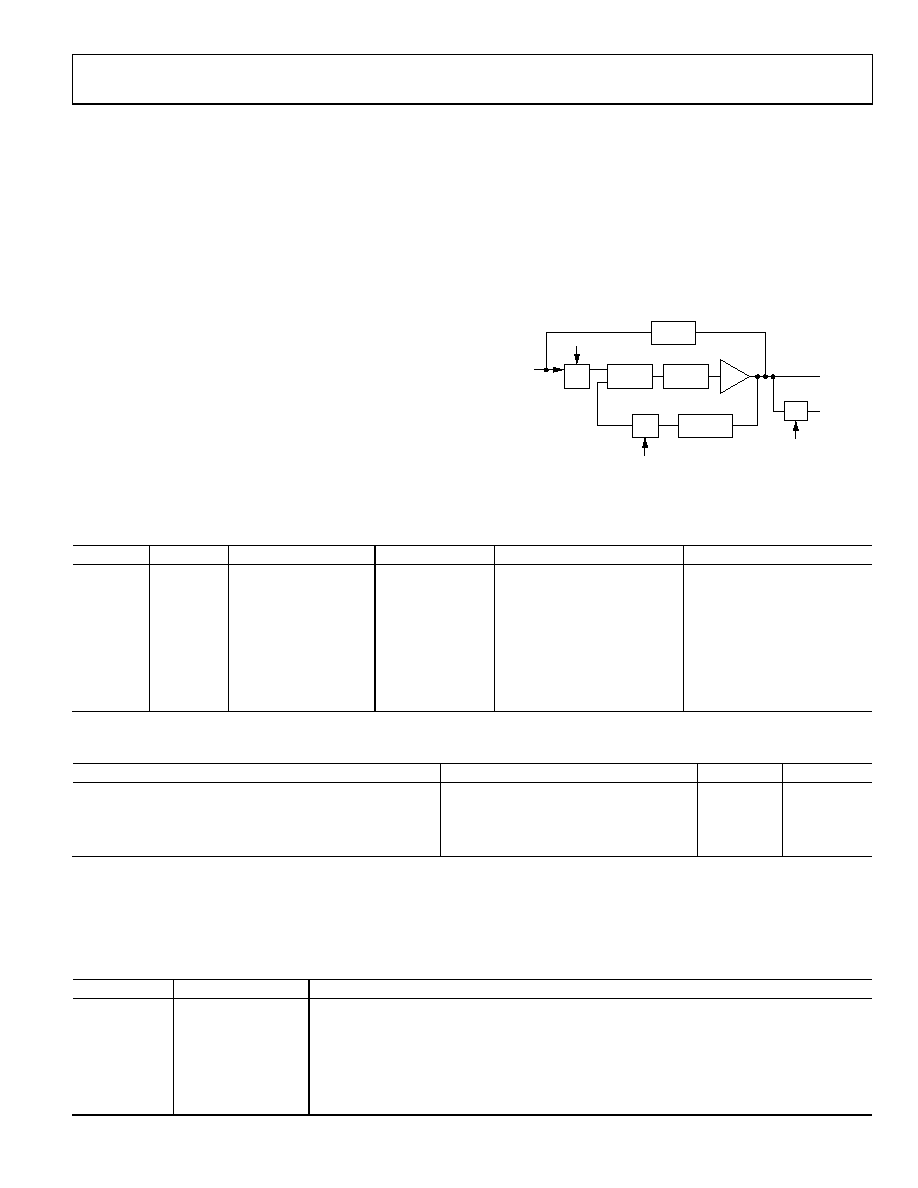

LPF

PHASE

DETECT

VCO

JCLK

HCLK

2

HCLKD

PLLMULT

2

LFB

2

IPD

BYPASS

MCLK

Figure 23. PLL Architecture and Control Functions

Table 21. Recommended PLL Register Settings

IPD

LFB

PLLMULT

HCLKD

HCLK

JCLK

0

N

0

N × MCLK

0

N

1

N × MCLK/2

N × MCLK

0

1

N

0

2 × N × MCLK

0

1

N

1

N × MCLK

2 × N × MCLK

1

0

N

0

N × MCLK/2

1

0

N

1

N × MCLK/4

N × MCLK/2

1

N

0

N × MCLK

1

N

1

N × MCLK/2

N × MCLK

Table 22. Recommended Values for PLL_HI and PLL_LO Registers

Video Standard

CLKIN Frequency on MCLK

PLL_HI

PLL_LO

SMPTE125M or ITU-R.BT656 (NTSC or PAL)

27 MHz

0x0008

0x0004

SMPTE293M (525p)

27 MHz

0x0008

0x0004

ITU-R.BT1358 (625p)

27 MHz

0x0008

0x0004

SMPTE274M (1080i)

74.25 MHz

0x0008

0x0084

HARDWARE BOOT

The boot mode can be configured via hardware using the CFG pins or via software (see the ADV202 User’s Guide). The first boot mode

after power-up is set by the CFG pins. Only Boot Mode 2, Boot Mode 4, and Boot Mode 6, described in Table 23, are available via hardware.

Table 23. Hardware Boot Modes

Boot Mode

Settings

Description

Hardware Boot

Mode 2

CFG[1] tied high,

CFG[2] tied low

No-Boot Host Mode. ADV202 does not boot, but all internal registers and memory are accessible

through normal host I/O operations.

For details, see the ADV202 User’s Guide and the Getting Started with the ADV202 application note.

Hardware Boot

Mode 4

CFG[1] tied low,

CFG[2] tied high

SoC Boot Mode.

Hardware Boot

Mode 6

CFG[1] and CFG[2]

tied high

Reserved.

相关PDF资料 |

PDF描述 |

|---|---|

| ADV601LCJSTZRL | IC CODEC VIDEO DSP/SRL 120LQFP |

| ADV202BBCZRL-115 | IC CODEC VIDEO 115MHZ 121CSPBGA |

| VI-JNH-IX-S | CONVERTER MOD DC/DC 52V 75W |

| VI-JN4-IX-S | CONVERTER MOD DC/DC 48V 75W |

| AD1928YSTZ-RL | IC CODEC 2ADC 8DAC W/PLL 48LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADV202BBCZ-135 | 功能描述:IC CODEC VIDEO 135MHZ 144CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADV202BBCZ-150 | 功能描述:IC VIDEO CODEC JPEG2000 144CSBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADV202BBCZ-157 | 制造商:Analog Devices 功能描述: |

| ADV202BBCZRL-115 | 功能描述:IC CODEC VIDEO 115MHZ 121CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADV202BBCZRL-150 | 功能描述:IC CODEC VIDEO 150MHZ 144CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。