参数资料

| 型号: | ADV7311KST |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/84页 |

| 文件大小: | 0K |

| 描述: | IC VID ENC 6-12BIT DAC'S 64LQFP |

| 产品变化通告: | ADV7xxx Obsolescence 16/Jan/2012 |

| 标准包装: | 1 |

| 类型: | 视频编码器 |

| 应用: | DVD,SD/HD |

| 电压 - 电源,模拟: | 2.5V |

| 电压 - 电源,数字: | 2.5V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

REV. A

–26–

ADV7310/ADV7311

LINE 313

LINE 314

LINE 1

tB

HSYNC

VSYNC

tA

tC

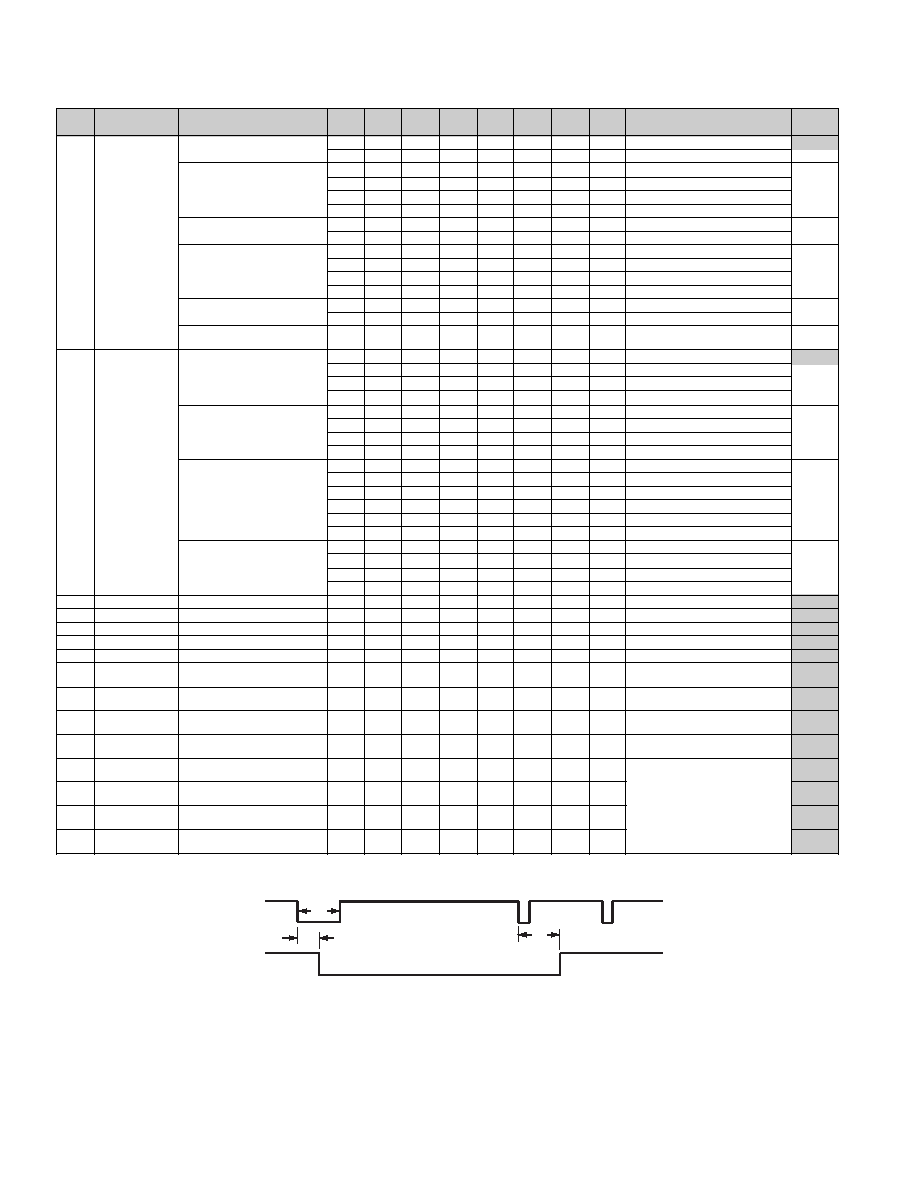

Figure 21. Timing Register 1 in PAL Mode

SR7–

SR0

Register

Bit Description

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Register Setting

Reset

Values

4Ah

SD Slave/Master Mode

0

Slave Mode

08h

1

Master Mode

SD Timing Mode

0

Mode 0

01

Mode 1

10

Mode 2

11

Mode 3

SD

BLANK Input

0

Enabled

1

Disabled

SD Luma Delay

0

No delay

01

2 clk cycles

10

4 clk cycles

11

6 clk cycles

SD Min. Luma Value

0

– 40 IRE

1– 7.5 IRE

SD Timing Reset

x

0

0000

0A low-high-low transition will reset

the internal SD timing counters

4Bh

SD

HSYNC Width

00

Ta = 1 clk cycle

00h

01

Ta = 4 clk cycles

10

Ta = 16 clk cycles

11

Ta = 128 clk cycles

SD

HSYNC to VSYNC delay

00

Tb = 0 clk cycle

01

Tb = 4 clk cycles

10

Tb = 8 clk cycles

11

Tb = 18 clk cycles

x0

Tc = Tb

x1

Tc = Tb + 32 us

00

1 clk cycle

01

4 clk cycles

10

16 clk cycles

11

128 clk cycles

HSYNC to Pixel Data Adjust

00

0 clk cycles

01

1 clk cycle

10

2 clk cycles

11

3 clk cycles

4Ch

SD FSC Register 0

xxx

xxxx

x

Subcarrier Frequency Bit 7–0

16h

4Dh

SD F

SC Register 1

xxx

xxxx

x

Subcarrier Frequency Bit 15–8

7Ch

4Eh

SD FSC Register 2

xxx

xxxx

x

Subcarrier Frequency Bit 23–16

F0h

4Fh

SD F

SC Register 3

xxx

xxxx

x

Subcarrier Frequency Bit 31–24

21h

50h

SD FSC Phase

xxx

xxxx

x

Subcarrier Phase Bit 9–2

00h

51h

SD Closed

Captioning

Extended Data on Even Fields

x

xxxx

x

Extended Data Bit 7–0

00h

52h

SD Closed

Captioning

Extended Data on Even Fields

x

xxxx

x

Extended Data Bit 15–8

00h

53h

SD Closed

Captioning

Data on Odd Fields

x

xxxx

x

Data Bit 7–0

00h

54h

SD Closed

Captioning

Data on Odd Fields

x

xxxx

x

Data Bit 15–8

00h

55h

SD Pedestal

Register 0

Pedestal on Odd Fields

17

16

15

14

13

12

11

10

00h

56h

SD Pedestal

Register 1

Pedestal on Odd Fields

25

24

23

22

21

20

19

18

00h

57h

SD Pedestal

Register 2

Pedestal on Even Fields

17

16

15

14

13

12

11

10

00h

58h

SD Pedestal

Register 3

Pedestal on Even Fields

25

24

23

22

21

20

19

18

00h

SD Timing

Register 0

SD Timing

Register 1

Setting any of these bits to 1 will

disable pedestal on the line number

indicated by the bit settings

SD

HSYNC to VSYNC Rising

Edge Delay [Mode 1 Only]

VSYNC Width [Mode 2 Only]

相关PDF资料 |

PDF描述 |

|---|---|

| ADV7321KSTZ | IC VID ENC 6-12BIT DAC'S 64LQFP |

| ADV7343BSTZ | IC ENCODER VIDEO W/DAC 64-LQFP |

| ADV7391BCPZ | IC ENCODER VIDEO W/DAC 32LFCSP |

| ADV7511KSTZ | IC XMITTER HDMI 12BIT 100LQFP |

| ADV7511WBSWZ | IC XMITTER HDMI AUTO 64LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADV7311KST | 制造商:Analog Devices 功能描述:Video IC |

| ADV7312 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multiformat 11-Bit HDTV Video Encoder |

| ADV7312KST | 制造商:AD 制造商全称:Analog Devices 功能描述:Multiformat 11-Bit HDTV Video Encoder |

| ADV7314 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs |

| ADV7314KST | 制造商:AD 制造商全称:Analog Devices 功能描述:Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs |

发布紧急采购,3分钟左右您将得到回复。