- 您现在的位置:买卖IC网 > PDF目录17104 > ADZS-BF533-MMSKIT (Analog Devices Inc)KIT STARTER MULTIMEDIA BF533 PDF资料下载

参数资料

| 型号: | ADZS-BF533-MMSKIT |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/64页 |

| 文件大小: | 0K |

| 描述: | KIT STARTER MULTIMEDIA BF533 |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services Multimedia Starter Kit |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | DSP:视频 |

| 适用于相关产品: | ADSP-BF533 |

| 所含物品: | 多媒体 SDK 光盘、子板和 ADSP-BF5xx EZ-LITE 评估板 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

�� �

�

�

�ADSP-BF531� /� ADSP-BF532� /� ADSP-BF533�

�Each� event� type� has� an� associated� register� to� hold� the� return�

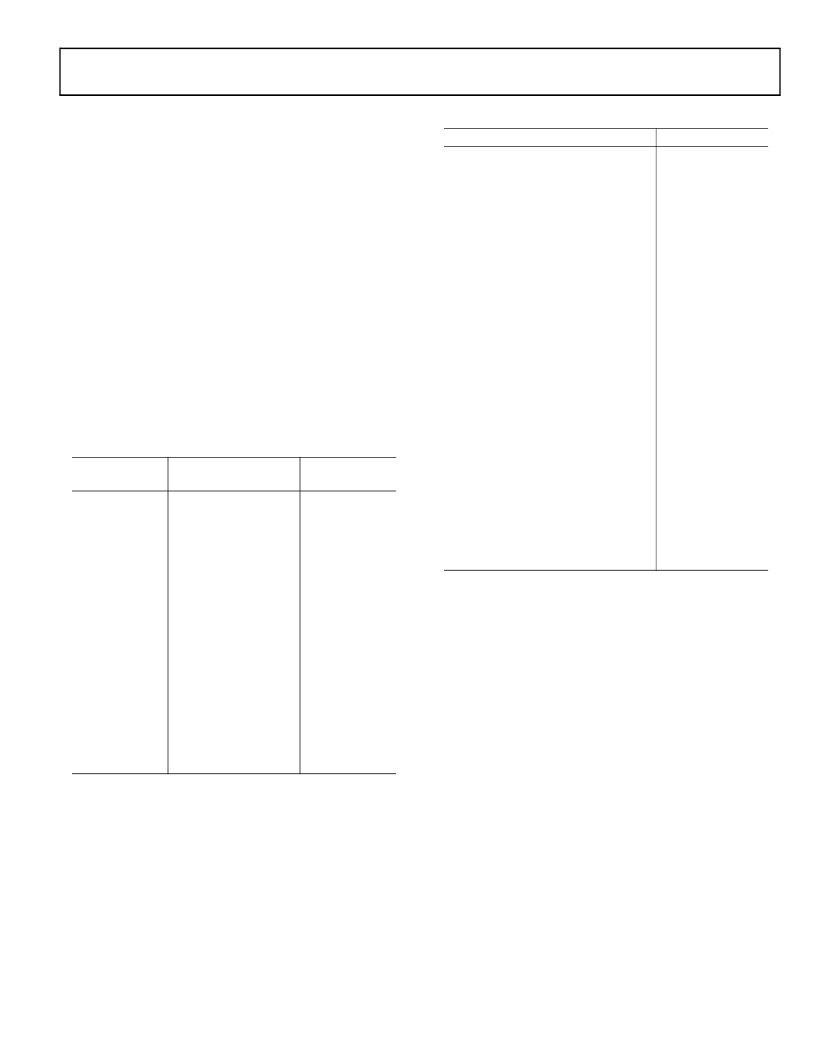

�Table� 3.� System� Interrupt� Controller� (SIC)�

�address� and� an� associated� return-from-event� instruction.� When�

�an� event� is� triggered,� the� state� of� the� processor� is� saved� on� the�

�supervisor� stack.�

�The� ADSP-BF531/ADSP-BF532/ADSP-BF533� processors’� event�

�controller� consists� of� two� stages,� the� core� event� controller� (CEC)�

�and� the� system� interrupt� controller� (SIC).� The� core� event� con-�

�troller� works� with� the� system� interrupt� controller� to� prioritize�

�and� control� all� system� events.� Conceptually,� interrupts� from� the�

�peripherals� enter� into� the� SIC,� and� are� then� routed� directly� into�

�the� general-purpose� interrupts� of� the� CEC.�

�Core� Event� Controller� (CEC)�

�The� CEC� supports� nine� general-purpose� interrupts� (IVG15� –7),�

�in� addition� to� the� dedicated� interrupt� and� exception� events.� Of�

�these� general-purpose� interrupts,� the� two� lowest� priority� inter-�

�rupts� (IVG15� –14)� are� recommended� to� be� reserved� for� software�

�interrupt� handlers,� leaving� seven� prioritized� interrupt� inputs� to�

�support� the� peripherals� of� the� processor.� Table� 2� describes� the�

�inputs� to� the� CEC,� identifies� their� names� in� the� event� vector�

�table� (EVT),� and� lists� their� priorities.�

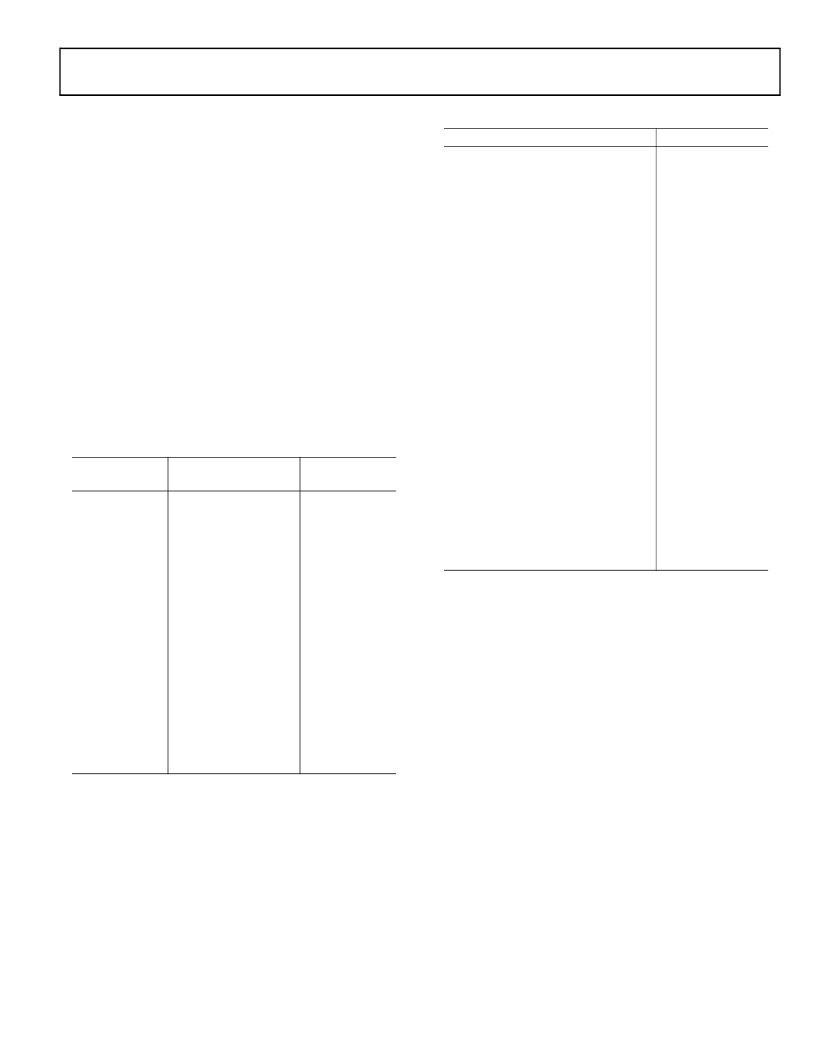

�Table� 2.� Core� Event� Controller� (CEC)�

�Peripheral� Interrupt� Event�

�PLL� Wakeup�

�DMA� Error�

�PPI� Error�

�SPORT� 0� Error�

�SPORT� 1� Error�

�SPI� Error�

�UART� Error�

�Real-Time� Clock�

�DMA� Channel� 0� (PPI)�

�DMA� Channel� 1� (SPORT� 0� Receive)�

�DMA� Channel� 2� (SPORT� 0� Transmit)�

�DMA� Channel� 3� (SPORT� 1� Receive)�

�DMA� Channel� 4� (SPORT� 1� Transmit)�

�DMA� Channel� 5� (SPI)�

�DMA� Channel� 6� (UART� Receive)�

�DMA� Channel� 7� (UART� Transmit)�

�Timer� 0�

�Default� Mapping�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG7�

�IVG8�

�IVG8�

�IVG9�

�IVG9�

�IVG9�

�IVG9�

�IVG10�

�IVG10�

�IVG10�

�IVG11�

�Priority�

�(0� is� Highest)�

�0�

�1�

�2�

�3�

�4�

�Event� Class�

�Emulation/Test� Control�

�Reset�

�Nonmaskable� Interrupt�

�Exception�

�Reserved�

�EVT� Entry�

�EMU�

�RST�

�NMI�

�EVX�

�Timer� 1�

�Timer� 2�

�Port� F� GPIO� Interrupt� A�

�Port� F� GPIO� Interrupt� B�

�Memory� DMA� Stream� 0�

�Memory� DMA� Stream� 1�

�Software� Watchdog� Timer�

�IVG11�

�IVG11�

�IVG12�

�IVG12�

�IVG13�

�IVG13�

�IVG13�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�Hardware� Error�

�Core� Timer�

�General� Interrupt� 7�

�General� Interrupt� 8�

�General� Interrupt� 9�

�General� Interrupt� 10�

�General� Interrupt� 11�

�General� Interrupt� 12�

�General� Interrupt� 13�

�General� Interrupt� 14�

�General� Interrupt� 15�

�IVHW�

�IVTMR�

�IVG7�

�IVG8�

�IVG9�

�IVG10�

�IVG11�

�IVG12�

�IVG13�

�IVG14�

�IVG15�

�Event� Control�

�The� processors� provide� a� very� flexible� mechanism� to� control� the�

�processing� of� events.� In� the� CEC,� three� registers� are� used� to�

�coordinate� and� control� events.� Each� register� is� 32� bits� wide:�

�?� CEC� interrupt� latch� register� (ILAT)� –� The� ILAT� register�

�indicates� when� events� have� been� latched.� The� appropriate�

�bit� is� set� when� the� processor� has� latched� the� event� and�

�cleared� when� the� event� has� been� accepted� into� the� system.�

�This� register� is� updated� automatically� by� the� controller,� but�

�it� can� also� be� written� to� clear� (cancel)� latched� events.� This�

�register� can� be� read� while� in� supervisor� mode� and� can� only�

�be� written� while� in� supervisor� mode� when� the� correspond-�

�ing� IMASK� bit� is� cleared.�

�System� Interrupt� Controller� (SIC)�

�The� system� interrupt� controller� provides� the� mapping� and� rout-�

�ing� of� events� from� the� many� peripheral� interrupt� sources� to� the�

�prioritized� general-purpose� interrupt� inputs� of� the� CEC.�

�Although� the� processors� provide� a� default� mapping,� the� user�

�can� alter� the� mappings� and� priorities� of� interrupt� events� by� writ-�

�ing� the� appropriate� values� into� the� interrupt� assignment�

�registers� (SIC_IARx).� Table� 3� describes� the� inputs� into� the� SIC�

�and� the� default� mappings� into� the� CEC.�

�?� CEC� interrupt� mask� register� (IMASK)� –� The� IMASK� regis-�

�ter� controls� the� masking� and� unmasking� of� individual�

�events.� When� a� bit� is� set� in� the� IMASK� register,� that� event� is�

�unmasked� and� is� processed� by� the� CEC� when� asserted.� A�

�cleared� bit� in� the� IMASK� register� masks� the� event,�

�preventing� the� processor� from� servicing� the� event� even�

�though� the� event� may� be� latched� in� the� ILAT� register.� This�

�register� can� be� read� or� written� while� in� supervisor� mode.�

�Note� that� general-purpose� interrupts� can� be� globally�

�enabled� and� disabled� with� the� STI� and� CLI� instructions,�

�respectively.�

�Rev.� I�

�|�

�Page� 7� of� 64� |�

�August� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| 0210390964 | CABLE JUMPER 1MM .030M 27POS |

| HMM06DRKI-S13 | CONN EDGECARD 12POS .156 EXTEND |

| GSM06DRKF-S13 | CONN EDGECARD 12POS .156 EXTEND |

| DC1546A | BOARD DAC LTC2754-16 |

| 0210490899 | CABLE JUMPER 1.25MM .030M 21POS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADZS-BF537-ASKIT | 功能描述:BOARD EVAL SKIT ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| ADZS-BF537-EZLITE | 功能描述:BOARD EVAL ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| ADZS-BF537-STAMP | 功能描述:SYSTEM DEV FOR ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| ADZS-BF537-STAMP | 制造商:Analog Devices 功能描述:Microcontroller Development Tool |

| ADZS-BF538-EZLITE | 制造商:Analog Devices 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。