参数资料

| 型号: | AGL125V5-FG144 |

| 厂商: | Microsemi SoC |

| 文件页数: | 154/250页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1KB FLASH 125K 144FBGA |

| 标准包装: | 160 |

| 系列: | IGLOO |

| 逻辑元件/单元数: | 3072 |

| RAM 位总计: | 36864 |

| 输入/输出数: | 97 |

| 门数: | 125000 |

| 电源电压: | 1.425 V ~ 1.575 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 144-LBGA |

| 供应商设备封装: | 144-FPBGA(13x13) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页当前第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页第229页第230页第231页第232页第233页第234页第235页第236页第237页第238页第239页第240页第241页第242页第243页第244页第245页第246页第247页第248页第249页第250页

Revision 23

5-1

5 – Datasheet Information

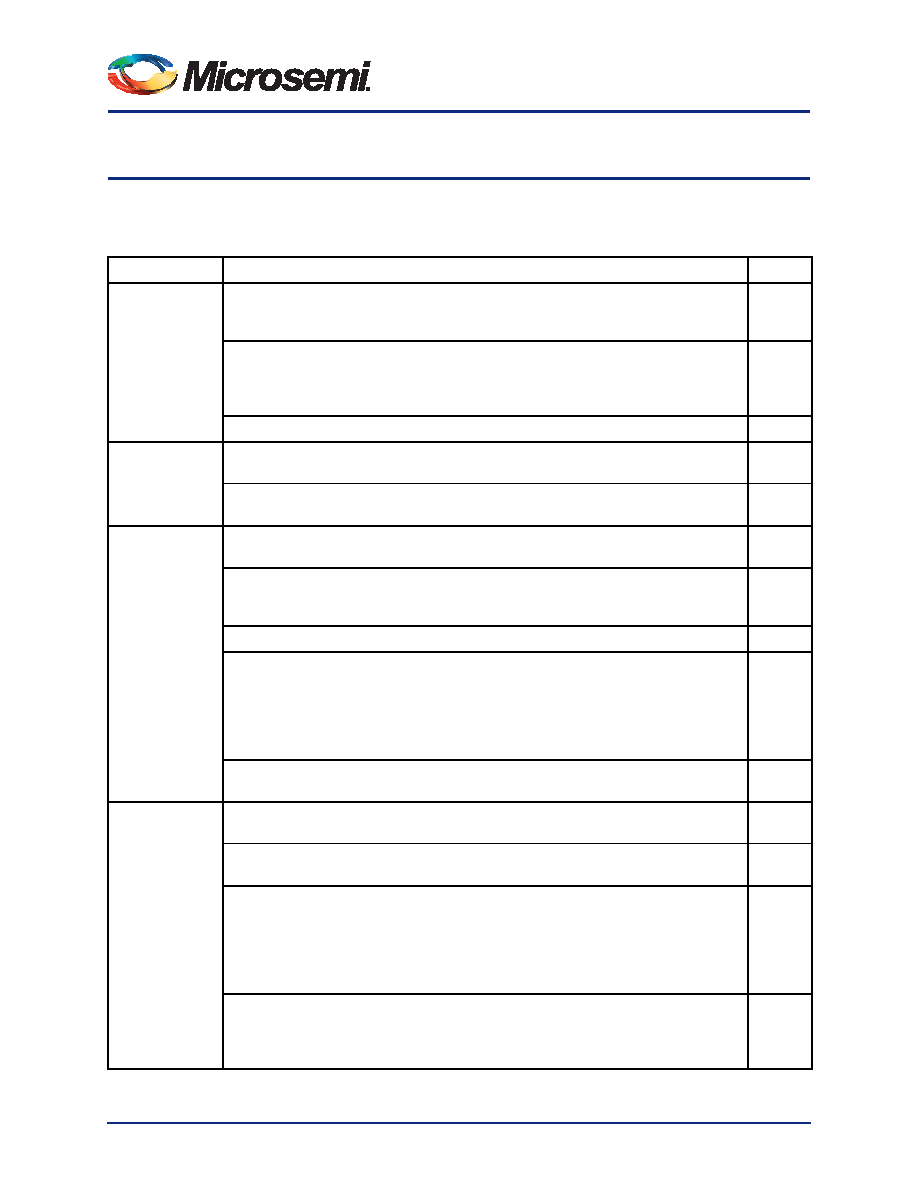

List of Changes

The following tables list critical changes that were made in each revision of the IGLOO datasheet.

Revision

Changes

Page

Revision 23

(December 2012)

The "IGLOO Ordering Information" section has been updated to mention "Y" as "Blank"

mentioning "Device Does Not Include License to Implement IP Based on the

Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43173).

The note in Table 2-189 IGLOO CCC/PLL Specification and Table 2-190 IGLOO

CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to

the online help associated with the core (SAR 42564).

Additionally, note regarding SSOs was added.

Live at Power-Up (LAPU) has been replaced with ’Instant On’.

NA

Revision 22

(September 2012)

The "Security" section was modified to clarify that Microsemi does not support read-

back of programmed data.

Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip

(SoC) throughout the document (SAR 40271).

N/A

Revision 21

(May 2012)

Under AGL125, in the Package Pin list, CS121 was incorrectly added to the datasheet

in revision 19 and has been removed (SAR 38217).

I to IV

Corrected the inadvertent error for Max Values for LVPECL VIH and revised the same

to ’3.6’ in Table 2-151 Minimum and Maximum DC Input and Output Levels (SAR

37685).

Figure 2-38 FIFO Read and Figure 2-39 FIFO Write have been added (SAR 34841).

The following sentence was removed from the VMVx description in the "Pin

Descriptions" section: "Within the package, the VMV plane is decoupled from the

simultaneous switching noise originating from the output buffer VCCI domain" and

replaced with “Within the package, the VMV plane biases the input stage of the I/Os in

the I/O banks” (SAR 38317). The datasheet mentions that "VMV pins must be

connected to the corresponding VCCI pins" for an ESD enhancement.

Pin description table for AGL125 CS121 was removed as it was incorrectly added to the

datasheet in revision 19 (SAR 38217).

-

Revision 20

(March 2012)

Notes indicating that AGL015 is not recommended for new designs have been added.

The "Devices Not Recommended For New Designs" section is new (SAR 35015).

Notes indicating that device/package support is TBD for AGL250-QN132 and

AGL060-FG144 have been reinserted (SAR 33689).

Values for the power data for PAC1, PAC2, PAC3, PAC4, PAC7, and PAC8 were

Dynamic Power Consumption in IGLOO Devices to match the SmartPower tool in

Libero software version 9.0 SP1 and Power Calculator spreadsheet v7a released on

08/10/2010 (SAR 33768).

The reference to guidelines for global spines and VersaTile rows, given in the "Global

Clock Contribution—PCLOCK" section, was corrected to the "Spine Architecture"

section of the Global Resources chapter in

(SAR 34730).

相关PDF资料 |

PDF描述 |

|---|---|

| A3P060-CS121I | IC FPGA 1KB FLASH 60K 121-CSP |

| BR24T64F-WE2 | IC EEPROM I2C 64K 400KHZ 8-SOP |

| A3P060-CSG121I | IC FPGA 1KB FLASH 60K 121-CSP |

| AGL030V2-CSG81I | IC FPGA 1KB FLASH 30K 81-CSP |

| A3PN060-2VQG100I | IC FPGA NANO 60K GATES 100-VQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AGL125V5-FG144I | 功能描述:IC FPGA 1KB FLASH 125K 144FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGL125V5-FGG144 | 功能描述:IC FPGA 1KB FLASH 125K 144FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGL125V5-FGG144I | 功能描述:IC FPGA 1KB FLASH 125K 144FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGL125V5-FQN144 | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:IGLOO Low-Power Flash FPGAs with Flash Freeze Technology |

| AGL125V5-FQN144ES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:IGLOO Low-Power Flash FPGAs with Flash Freeze Technology |

发布紧急采购,3分钟左右您将得到回复。