参数资料

| 型号: | AGLP125V5-CSG289 |

| 厂商: | Microsemi SoC |

| 文件页数: | 53/134页 |

| 文件大小: | 0K |

| 描述: | IC FPGA IGLOO PLUS 125K 289-CSP |

| 标准包装: | 152 |

| 系列: | IGLOO PLUS |

| 逻辑元件/单元数: | 3120 |

| RAM 位总计: | 36864 |

| 输入/输出数: | 212 |

| 门数: | 125000 |

| 电源电压: | 1.425 V ~ 1.575 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 289-TFBGA,CSBGA |

| 供应商设备封装: | 289-CSP(14x14) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页

IGLOO PLUS Low Power Flash FPGAs

Revision 16

2-11

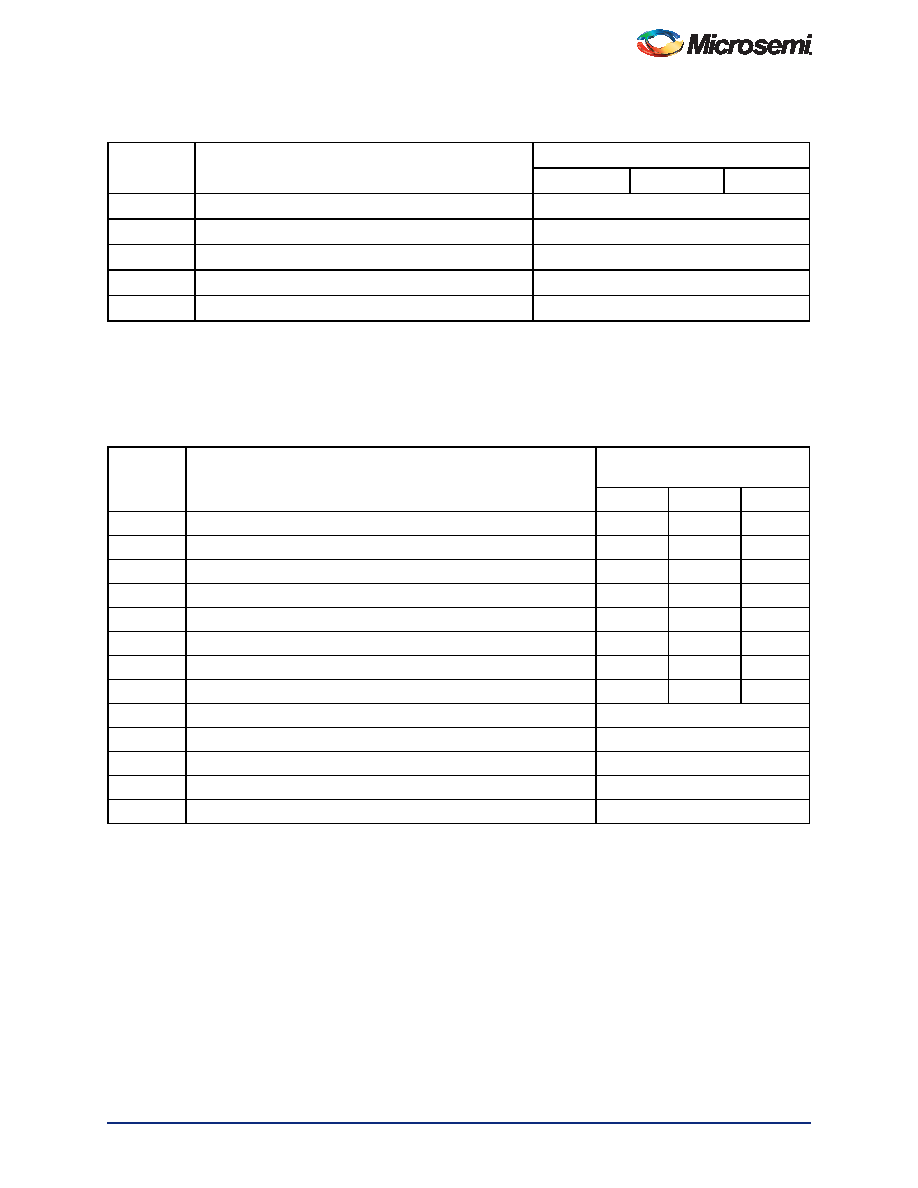

Table 2-16 Different Components Contributing to the Static Power Consumption in IGLOO PLUS Devices

For IGLOO PLUS V2 or V5 Devices, 1.5 V Core Supply Voltage

Parameter

Definition

Device-Specific Static Power (mW)

AGLP125

AGLP060

AGLP030

PDC1

Array static power in Active mode

PDC2

Array static power in Static (Idle) mode

PDC3

Array static power in Flash*Freeze mode

PDC4

Static PLL contribution

1.841

PDC5

Bank quiescent power (VCCI-dependent)

Notes:

1. This is the minimum contribution of the PLL when operating at lowest frequency.

2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet

calculator or the SmartPower tool in Libero SoC software.

Table 2-17 Different Components Contributing to Dynamic Power Consumption in IGLOO PLUS Devices

For IGLOO PLUS V2 Devices, 1.2 V Core Supply Voltage

Parameter

Definition

Device-Specific Dynamic Power

(W/MHz)

AGLP125 AGLP060 AGLP030

PAC1

Clock contribution of a Global Rib

2.874

1.727

0.0001

PAC2

Clock contribution of a Global Spine

1.264

1.244

2.241

PAC3

Clock contribution of a VersaTile row

0.963

0.975

0.981

PAC4

Clock contribution of a VersaTile used as a sequential module

0.098

0.096

PAC5

First contribution of a VersaTile used as a sequential module

0.018

PAC6

Second contribution of a VersaTile used as a sequential module

0.203

PAC7

Contribution of a VersaTile used as a combinatorial module

0.160

0.170

0.158

PAC8

Average contribution of a routing net

0.679

0.686

0.748

PAC9

Contribution of an I/O input pin (standard-dependent)

PAC10

Contribution of an I/O output pin (standard-dependent)

PAC11

Average contribution of a RAM block during a read operation

25.00

PAC12

Average contribution of a RAM block during a write operation

30.00

PAC13

Dynamic contribution for PLL

2.10

Note: 1. There is no Center Global Rib present in AGLP030, and thus it starts directly at the spine resulting in

0W/MHz.

相关PDF资料 |

PDF描述 |

|---|---|

| AGLP125V5-CS289 | IC FPGA IGLOO PLUS 125K 289-CSP |

| M1AGL250V2-VQ100I | IC FPGA 1KB FLASH 250K 100-VQFP |

| M1AGL250V2-VQG100I | IC FPGA 1KB FLASH 250K 100-VQFP |

| AGL250V2-VQG100I | IC FPGA 1KB FLASH 250K 100VQFP |

| AGL250V2-VQ100I | IC FPGA 1KB FLASH 250K 100VQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AGLP125-V5CSG289ES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP125-V5CSG289I | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP125V5-CSG289I | 功能描述:IC FPGA IGLOO PLUS 125K 289-CSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO PLUS 标准包装:90 系列:ProASIC3 LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:36864 输入/输出数:157 门数:250000 电源电压:1.425 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 125°C 封装/外壳:256-LBGA 供应商设备封装:256-FPBGA(17x17) |

| AGLP125-V5CSG289PP | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP125V5-FCS281 | 制造商:Microsemi Corporation 功能描述:FPGA IGLOO PLUS 125K GATES 1024 CELLS 130NM 1.5V 281CSP - Trays |

发布紧急采购,3分钟左右您将得到回复。