- 您现在的位置:买卖IC网 > PDF目录166132 > AK8850 (Asahi Kasei Microsystems Co.,Ltd) NTSC Digital Video Decoder PDF资料下载

参数资料

| 型号: | AK8850 |

| 厂商: | Asahi Kasei Microsystems Co.,Ltd |

| 英文描述: | NTSC Digital Video Decoder |

| 中文描述: | NTSC制式数字视频解码器 |

| 文件页数: | 76/99页 |

| 文件大小: | 1757K |

| 代理商: | AK8850 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

ASAHI KASEI

[AK8850]

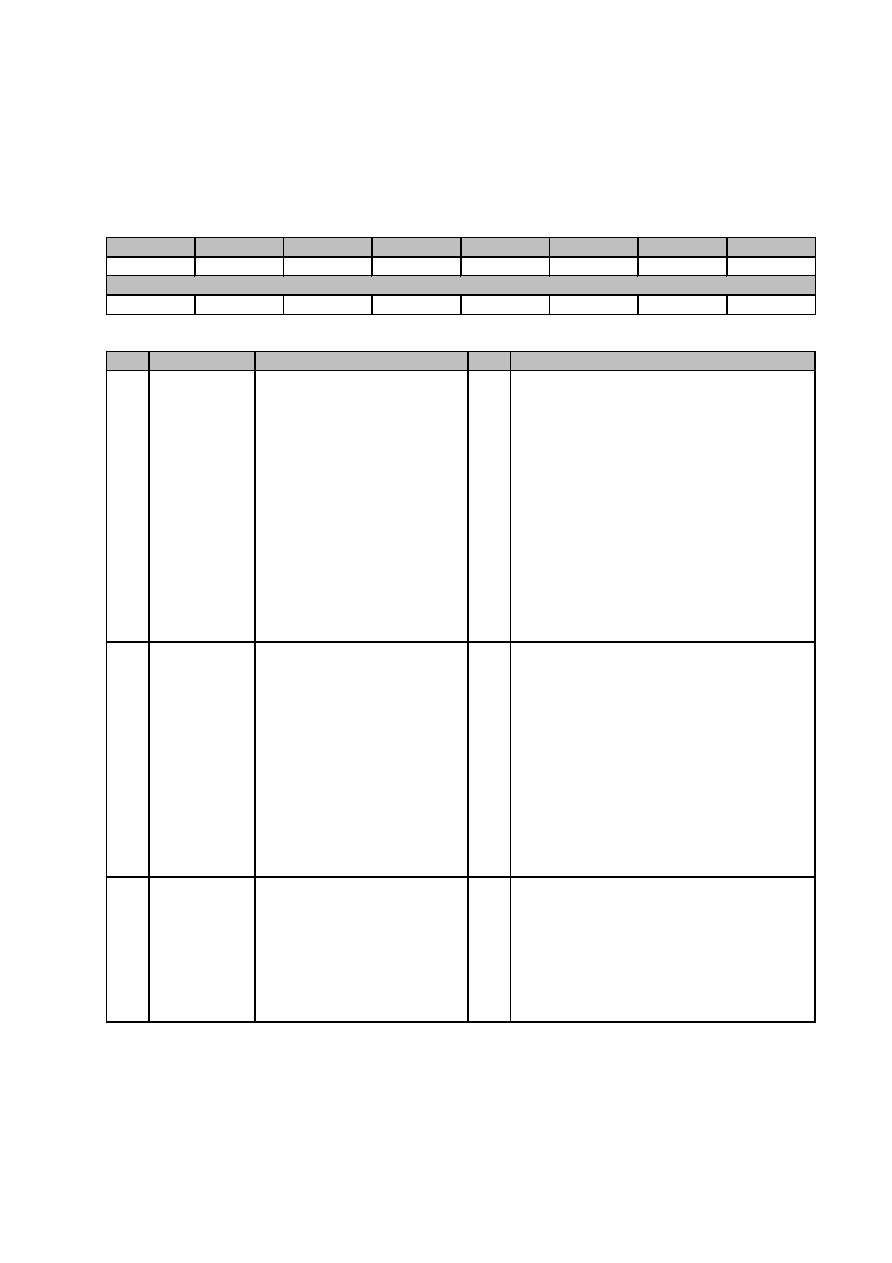

CLAMP TIMING 1 CONTROL REGISTER ( R / W ) [ SUB ADDRESS 0x0B ]

This register sets SYNC-TIP Clamp timing. Clamp Timing Pulse generation and its pulse width can be adjusted.

Output signal mode selection of the EXTCLP pin is also possible. For a timing diagram, refer to the SYNC Separation

description in the Clamp section. Reserved bits must be set to “ 0 “.

Sub Address 0x0B

Default Value : 0x11

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

EXTCLP1

EXTCLP0

SCLPWIDTH2

SCLPWIDTH1

SCLPWIDTH0

SCLPSTAT2

SCLPSTAT1

SCLPSTAT0

Default Value

0

1

0

1

Clamp Timing Control Register

BIT

Register Name

R/W

Definition

Setting the start position of synctip clamp pulse

bit 0

SCLPSTAT0

SCLPSTAT2

default value is

SCLPSTA2 : SCLPSTA0 = 001

[SCLPSTAT2 SCLPSTAT0 ]

000 : 2clks later

001 : 4clks later

011 : 8clks later

100 : 10clks later

101 : 12clks later

111 : 16clks later

1clk is about 37[nsec]

R/W

Synctip Clamp Start timing0

Synctip Clamp Start timing2 bit

bit 2

010 : 6clks later

110 : 14clks later

SCLPWIDTH0

Synctip Clamp Pulse Width0 bit

Synctip Clamp Pulse Width2 bit

R/W

SCLPWIDTH2 : SCLPWIDTH0 = 010.

[SCLPWIDTH3 SCLPWIDTH0]

001 : 4 clks (148nsec)

010 : 8 clks (296nsec)

011 : 16 clks (592nsec)

100 : 24 clks (888nsec)

101 : 32 clks (1.18usec)

110 : 40 clks (1.48usec)

111 :48 clks (1.78usec)

Setting the synctip clamp pulse width

Default value is

bit 3

SCLPWIDTH2

bit 5

000 : 2 clks (74nsec)

bit 6

Setting the output the timing data from

EXTCLP-pin.

00 : Hi-Z (Defaul)

11 : SYNCDET signal

R/W

External Clamp 0 bit

EXTCLP0

External Clamp 1 bit

EXTCLP1

bit 7

[EXTCLP1:EXTCLP0]

01 : Internal synctip clamp timing pulse.

10 : Internal pedestal clamp timing pulse.

Rev.0

78

2003/01

相关PDF资料 |

PDF描述 |

|---|---|

| AKA103 | 16 SEG ALPHANUMERIC DISPLAY, SUPER BRIGHT ORANGE, 25.4 mm |

| AKD4112B | AKD4112B EVALUATION BOARD |

| AKD4552 | 3V 96KHZ 24BIT CODEC |

| AKD4640 | AKD4640 EVALUATION BOARD |

| AL-12-60 | 12 A, SILICON, BRIDGE RECTIFIER DIODE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AK-8850 | 功能描述:机架和机柜配件 ANCHOR KIT SEISMIC R RoHS:否 制造商:Bivar 产品:Rack Accessories 面板空间: 颜色:Black |

| AK8851 | 制造商:AKM 制造商全称:AKM 功能描述:NTSC/PAL/SECAM Digital Video Decoder |

| AK8851VQ | 制造商:AKM 制造商全称:AKM 功能描述:NTSC/PAL/SECAM Digital Video Decoder |

| AK8853VN | 制造商:AKM 制造商全称:AKM 功能描述:NTSC/PAL/SECAM Digital Video Decoder |

| AK8853XQ | 制造商:AKM 制造商全称:AKM 功能描述:NTSC/PAL/SECAM Digital Video Decoder |

发布紧急采购,3分钟左右您将得到回复。