- 您现在的位置:买卖IC网 > PDF目录378309 > AL4CX3660 (AverLogic Technologies, Inc.) 2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs PDF资料下载

参数资料

| 型号: | AL4CX3660 |

| 厂商: | AverLogic Technologies, Inc. |

| 英文描述: | 2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs |

| 中文描述: | 2K / 4K的/ 8K的/ 16K的/ 32K的× 36同步FIFO的 |

| 文件页数: | 2/2页 |

| 文件大小: | 41K |

| 代理商: | AL4CX3660 |

A

VER

L

OGIC

T

ECHNOLOGIES

,

I

NC

.

E-mail: sales_usa@averlogic.com

A

VER

L

OGIC

T

ECHNOLOGIES

,

C

ORP

.

E-mail: sales@averlogic.com.tw URL: www.averlogic.com.tw

URL: www.averlogic.com

February 24, 2003

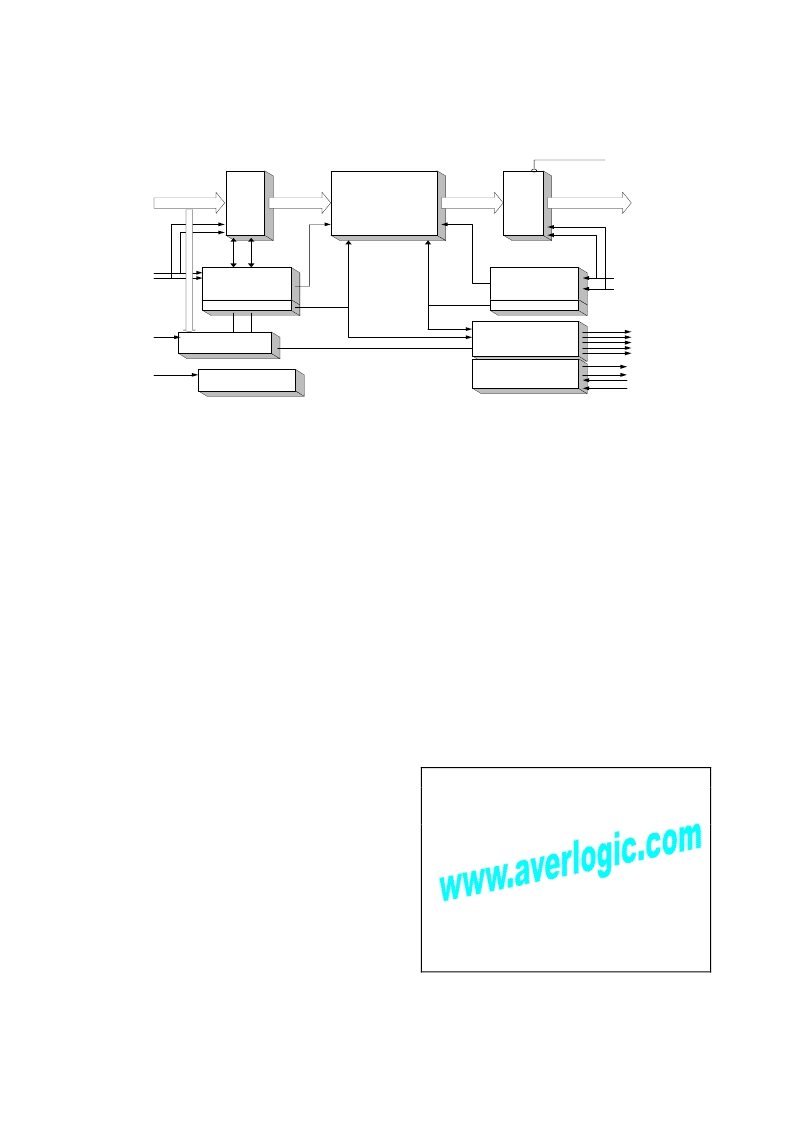

M e m o r y A r r a y

2 K x 3 6 , 4 K x 3 6 ,

8 K x 3 6 , 1 6 K x 3 6 ,

3 2 K x 3 6

In p u t

B u ffe r

O u tp u t

B u ffe r

W r ite C o n tr o l

L o g ic

R e a d C o n tr o l

L o g ic

F la g L o g ic

E x p a n s io n L o g ic

W r ite P o in te r

R e a d P o in te r

O ffs e t R e g is s e r s

R e s e t L o g ic

In p u t d a ta b u s

O u tp u t d a ta b u s

/O E

W C L K

/W E N

/L D

/R S T

R C L K

/R E N

/F F

/E F

/P A F

/P A E

/W X O

/R X O

/W X I

/R X I

A L 4 C X 3 6 x 0 F IF O B lo c k D ia g r a m

The embedded memory array with built-in

address decoder, pointer manager and state-

of-the-art circuits provide an easy-to-use

interface to serial read/write memory and

offer a flexible way to manage memory in the

system design.

The input port of the FIFO is controlled by a

free running clock (WCLK), and an input

enable (/WEN). The output port is controlled

by another clock (RCLK) and an output

enable (/REN). Data is read into or output

from FIFO synchronous on every individual

WRCK or RCLK clock cycle when /WEN or

/REN is asserted respectively.

These FIFOs support selectable bus width up

to 36bit for both input and output ports and

can be configured as x36 to x36, x36 to x18,

x36 to x9, x18 to x36 and x9 to x36 multiple

input and output port bus width. This allows

for easy conversion of the bus width between

the input flow and output flow.

There are two fixed flags, Empty Flag/Output

Ready and Full Flag/Input Ready, and two

programmable flags, Almost-Empty and

Almost-Full.

manipulation of the synchronous control.

Multiple AL4CX36x0s can be cascaded to

expand the storage depth or can be used in

parallel to expand bus width.

The FIFOs are 3.3-volt devices with 5-volt

input tolerance. And are available in the 128-

pin thin quad flat Pack (TQFP Package).

The

flags

enable

further

D

ISTRIBUTED BY

:

相关PDF资料 |

PDF描述 |

|---|---|

| AL4CX3670 | 2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs |

| AL4CX3680 | 2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs |

| AL4CX3690 | 2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs |

| AL4V183 | 16K, 64K-Bit Line FIFO |

| AL4V185 | 16K, 64K-Bit Line FIFO |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AL4CX3670 | 制造商:AVERLOGIC 制造商全称:AVERLOGIC 功能描述:2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs |

| AL4CX3680 | 制造商:AVERLOGIC 制造商全称:AVERLOGIC 功能描述:2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs |

| AL4CX3690 | 制造商:AVERLOGIC 制造商全称:AVERLOGIC 功能描述:2K/ 4K/ 8K/ 16K/ 32K x 36 Synchronous FIFOs |

| AL4P | 制造商:Thomas & Betts 功能描述:AL COMPR TERMINAL |

| AL4V183 | 制造商:AVERLOGIC 制造商全称:AVERLOGIC 功能描述:16K, 64K-Bit Line FIFO |

发布紧急采购,3分钟左右您将得到回复。