- 您现在的位置:买卖IC网 > PDF目录378403 > AN-5061 (Fairchild Semiconductor Corporation) Layout Guidelines PDF资料下载

参数资料

| 型号: | AN-5061 |

| 厂商: | Fairchild Semiconductor Corporation |

| 英文描述: | Layout Guidelines |

| 中文描述: | 布局指南 |

| 文件页数: | 2/4页 |

| 文件大小: | 138K |

| 代理商: | AN-5061 |

AN-5061

APPLICATION NOTE

2004 Fairchild Semiconductor Corporation

Rev. 1.0.3 4/30/07

www.fairchildsemi.com

2

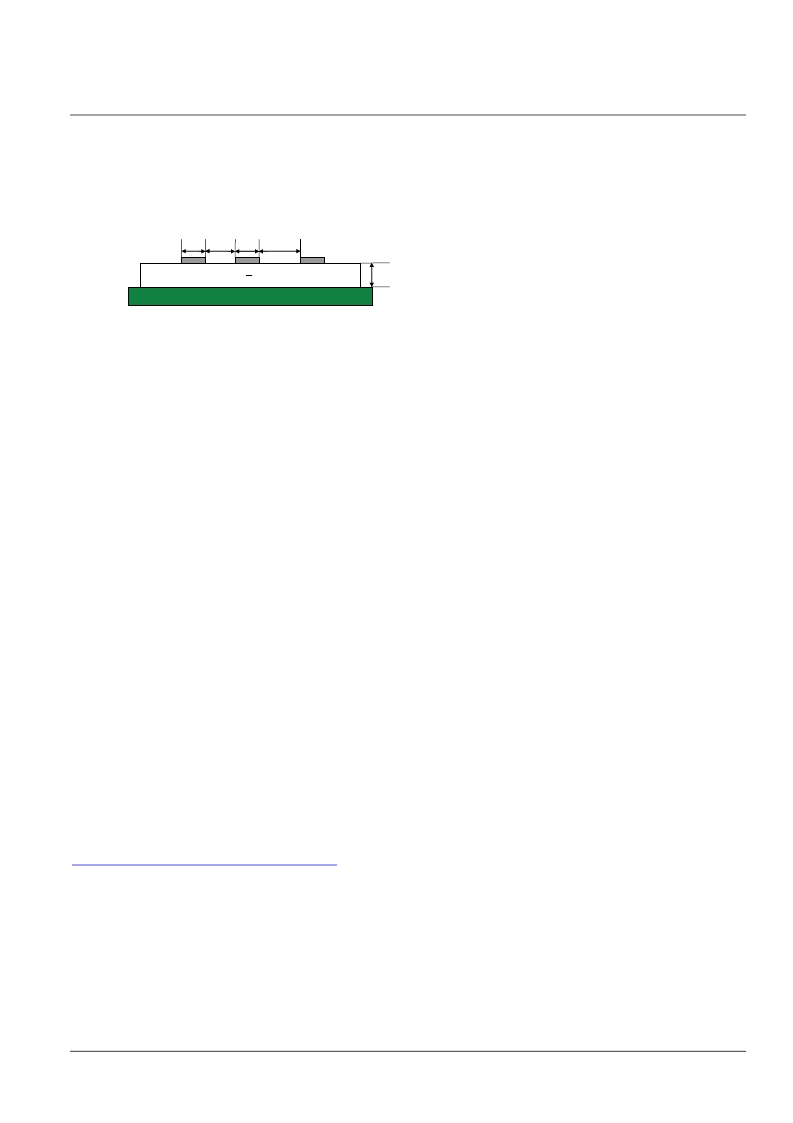

If close coupling of the differential pairs is desired, the main

consideration is to keep (S<H) and (X>5H) (see Figure 2).

The important factor is that industry-standard equations are

used to determine the proper dimensions to maintain a

design goal or constant 100

Ω

differential impedance.

Layer 2 (GND)

Layer 1 (TOP)

W

S

W

Dielectric

X

H

+

CLK

Figure 2.

Differential Pair Coupling

External termination of the differential pair is not necessary

because the μSerDes devices have internal termination.

When operating in unidirectional mode of the FIN12 and

FIN24, the CKSO outputs of the deserializer and the CKSI

inputs of the serializer are not needed. To minimize power

consumption, the CKSO outputs should be allowed to float

and no termination resistor should be connected. The status

of the CKSI inputs is dependent on the specific device

being used. All versions of μSerDes devices can have the

CKSI inputs either floating or grounded. Both the (+) and

(-) CKSI signals should be tied to the same potential

whether floating or grounded.

Flex Cable

When working with flex cable as an interface media

between the serializer and deserializer, it is important to

minimize any discontinuities that may affect the signal

integrity of the serial clock and data lines. The objective is

to maintain a differential impedance of 100

Ω

throughout the

serial link. Since there are various pitches of Flat Flex Cable

(FFC), with and without GND shielding, there are specific

signal configurations that should be followed to create the

desired 100

Ω

impedance. For instance, when working with

a 1mm pitch, unshielded flex cable, it is recommended to

route with a GND-SIG1-SIG2-GND arrangement, where

SIG1 and SIG2 are the positive and negative signals of the

differential pair. MERITEC

developed the paper

“Impedance Tests of Meritec’s Laminated Flat Cable and

Teflon Ribbon Cable (FRC)” that outlines the impedance of

several types of flex cable with various combinations of

signal configurations. The paper can be reviewed at:

http://www.meritec.com/pdf/FFCImpTest187.pdf

Parallel Clock and Data Routing

The primary consideration with clock and I/O data is to

route them in a manner that reduces capacitive and

inductive crosstalk, while maintaining equivalent length

(within system timing tolerances).

Inductive crosstalk can be reduced by at least maintaining

an (X>5H) edge to edge separation between all traces (see

Figure 2). This is a minimum recommendation and any

distance X greater than 5H results in an even greater

decrease in coupling.

Limit the length of parallel trace routes. Longer parallel

lengths increase the mutual inductance and the crosstalk.

Capacitive crosstalk can be reduced by routing traces on

adjacent signal layers at right angles.

To reduce the radiated emissions, as well as the

susceptibility to EMI, route clock traces on stripline layers.

Where termination is necessary, it is better to use smaller

surface mount components (ex. 0603 package) for lower

lead inductance and pad capacitance.

If operating as a serializer in PLL-bypass mode of FIN12 or

FIN24, the CKREF signal should be connected to GND and

a free-running bit clock connected to the CKSI differential

inputs. Refer to the datasheet for more information on PLL-

bypass mode.

When operating in unidirectional mode of FIN12 or FIN24,

the deserializer CKREF and STROBE signals should be

connected to GND.

Unused data inputs should either be connected to ground or

V

DDP

for the FIN12 or FIN24. To minimize dynamic power

due to data transitions, it is recommended that the unused

signals be grouped together and tied to the same polarity.

Unused output signals should be allowed to float.

Control I/O

The DIRI input pin is used to control the direction of data

flow through certain μSerDes devices (FIN24, FIN12). If

DIRI=0, the device is a deserializer; if DIRI=1, the device is

a serializer. DIRO is an output pin that generates the

complementary state of DIRI. The DIRO pin can be used in

bi-directional applications where the system drives the DIRI

pin of the master device and the DIRO pin of the master

device can be connected to the DIRI pin of the slave device.

The DIRO pin should be left floating if not used.

The functionality of S1 and S2 control pins is dependent on

the μSerDes device being used. For example, the S1 and S2

pins control the direction of DP[21:24] data signals for the

FIN24 device. For the FIN24A device, the S1 and S2 pins

are used to define the frequency range of the CKREF input

clock. Driving S1 and S2 low results in a power down and

reset of the device.

Notes:

1.

CKREF input frequency of the FIN24 device is

internally set for operation between 10 and 30MHz.

2.

The DP[21:22] input pins of the FIN24A serializer

device are always outputs on the corresponding

DP[23:24] pins of the deserializer device.)

相关PDF资料 |

PDF描述 |

|---|---|

| AN-53 | Implementing an RC5051 DC-DC Converter on Pentium II Motherboards |

| AN-6003 | Shoot-through in Synchronous Buck Converters |

| AN-6006 | LJT 19C 19#20 PIN WALL RECP |

| AN-60 | Application Note 60 (TMC22x5y input data ranges) |

| AN-7508 | LJT 37C 37#22D PIN WALL RECP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AN506-6-10 | 制造商:NEW SURPLUS HARDWARE 功能描述: |

| AN5070 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TV Switch Circuit |

| AN5071 | 制造商:Panasonic Industrial Company 功能描述:IC |

| AN5072 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TV Switch Circuit |

| AN507-428R8 | 制造商:AN# - MILITARY 功能描述: |

发布紧急采购,3分钟左右您将得到回复。