参数资料

| 型号: | APA1000-CQ352B |

| 厂商: | Microsemi SoC |

| 文件页数: | 93/178页 |

| 文件大小: | 0K |

| 描述: | IC FPGA PROASIC+ 1M 352-CQFP |

| 标准包装: | 1 |

| 系列: | ProASICPLUS |

| RAM 位总计: | 202752 |

| 输入/输出数: | 248 |

| 门数: | 1000000 |

| 电源电压: | 2.3 V ~ 2.7 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 352-BFCQFP,带拉杆 |

| 供应商设备封装: | 352-CQFP(75x75) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页当前第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页

ProASICPLUS Flash Family FPGAs

v5.9

2-11

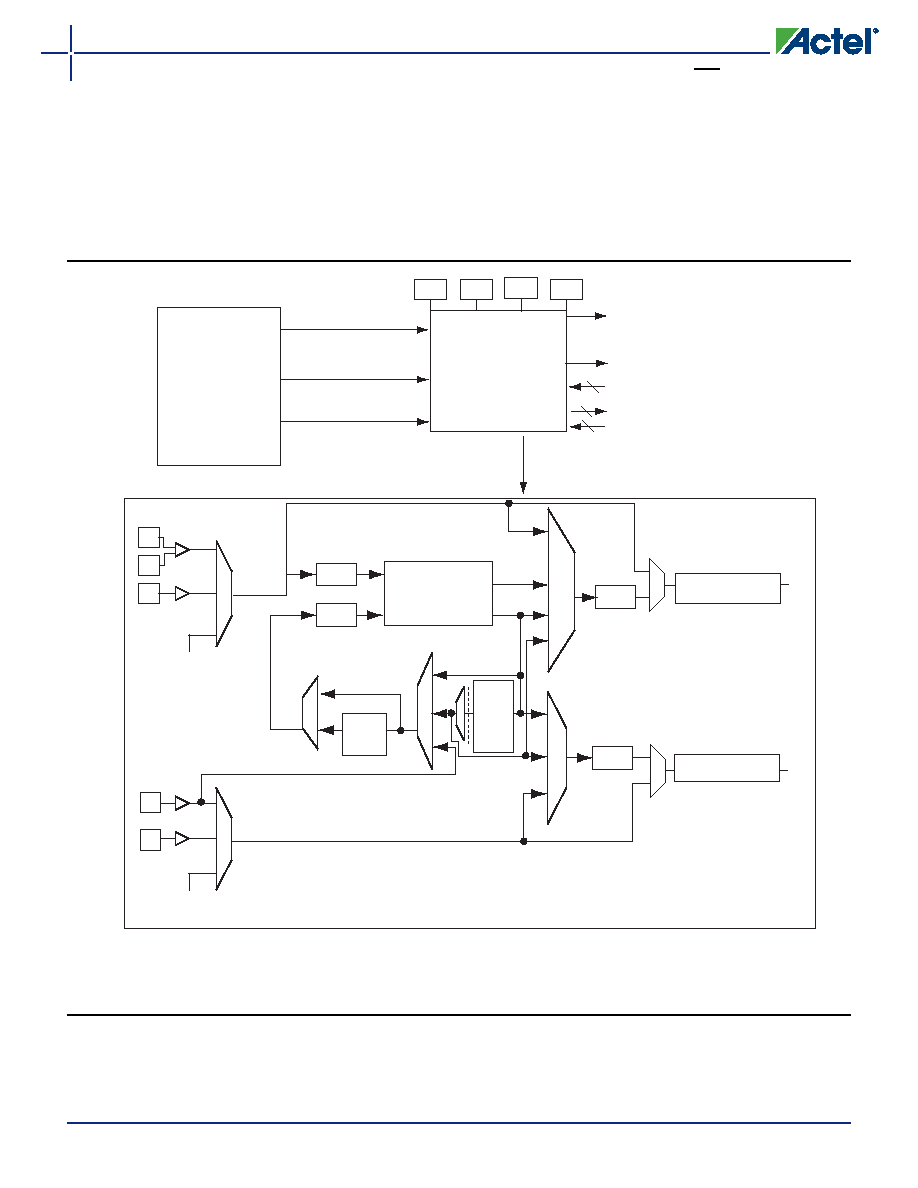

The clock conditioning circuit can advance or delay the

clock up to 8 ns (in increments of 0.25 ns) relative to the

positive edge of the incoming reference clock. The system

also allows for the selection of output frequency clock

phases of 0° and 180°.

Prior to the application of signals to the rib drivers, they

pass through programmable delay units, one per global

network. These units permit the delaying of global

signals relative to other signals to assist in the control of

input set-up times. Not all possible combinations of input

and output modes can be used. The degrees of freedom

available in the bidirectional global pad system and in

the clock conditioning circuit have been restricted. This

avoids unnecessary and unwieldy design kit and software

work.

Notes:

1. FBDLY is a programmable delay line from 0 to 4 ns in 250 ps increments.

2. DLYA and DLYB are programmable delay lines, each with selectable values 0 ps, 250 ps, 500 ps, and 4 ns.

3. OBDIV will also divide the phase-shift since it takes place after the PLL Core.

Figure 2-11 PLL Block – Top-Level View and Detailed PLL Block Diagram

AVDD

AGND

GND

+

-

VDD

External Feedback Signal

GLA

GLB

Dynamic

Configuration Bits

Flash

Configuration Bits

8

27

4

Clock Conditioning

Circuitry

(Top level view)

Global MUX A OUT

Global MUX B OUT

See Figure 2-15

on page 2-15

Input Pins to the PLL

GLB

GLA

÷u

÷v

PLL Core

0°

180°

0

1

6

7

5

4

2

Delay Line 0.0 ns, 0.25 ns,

0.50 ns and 4.00 ns

P+

P-

Clock from Core

(GLINT mode)

CLK

1

0

Deskew

Delay

2.95 ns

1

2

3

Delay Line

0.25 ns to

4.00 ns,

16 steps,

0.25 ns

increments

3

1

2

Delay Line 0.0 ns, 0.25 ns,

0.50 ns and 4.00 ns

Clock from Core

(GLINT mode)

CLKA

EXTFB

XDLYSEL

Bypass Secondary

Bypass Primary

FIVDIV[4:0]

FBDIV[5:0]

FBSEL[1:0]

OAMUX[1:0]

DLYA[1:0]

DLYB[1:0]

OBDIV[1:0]

OBMUX[2:0]

OADIV[1:0]

FBDLY[3:0]

÷n

÷m

Clock Conditioning Circuitry Detailed Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| APA1000-LG624B | IC FPGA PROASIC+ 1M 624-LGA |

| EP4SE820F43I4 | IC STRATIX IV FPGA 820K 1760FBGA |

| EP4SE820F43C3 | IC STRATIX IV FPGA 820K 1760FBGA |

| 24AA32AT/SM | IC EEPROM 32KBIT 400KHZ 8SOIC |

| 11LC161T-E/MNY | IC EEPROM 16K SER AUTO 8TDFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| APA1000-CQ352M | 制造商:Microsemi Corporation 功能描述:FPGA ProASICPLUS Family 1M Gates 180MHz 0.22um Technology 2.5V 352-Pin CQFP 制造商:Microsemi Corporation 功能描述:FPGA PROASICPLUS 1M GATES 180MHZ 0.22UM 2.5V 352CQFP - Trays |

| APA1000-CQB | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA1000-CQES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA1000-CQGB | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA1000-CQGES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。