- 您现在的位置:买卖IC网 > PDF目录381325 > AS7C31024-12TJC (ALLIANCE SEMICONDUCTOR CORP) AML41 Series, Solid State Indicator, Rectangular, Pushbutton Style, Lighted, 2 Incandescent Lamp, Snap in panel mount PDF资料下载

参数资料

| 型号: | AS7C31024-12TJC |

| 厂商: | ALLIANCE SEMICONDUCTOR CORP |

| 元件分类: | DRAM |

| 英文描述: | AML41 Series, Solid State Indicator, Rectangular, Pushbutton Style, Lighted, 2 Incandescent Lamp, Snap in panel mount |

| 中文描述: | 128K X 8 STANDARD SRAM, 12 ns, PDSO32 |

| 封装: | 0.300 INCH, PLASTIC, SOJ-32 |

| 文件页数: | 2/9页 |

| 文件大小: | 208K |

| 代理商: | AS7C31024-12TJC |

2

ALLIANCE SEMICONDUCTOR

11/29/00

AS7C1024

AS7C31024

Functional description

The AS7C1024 and AS7C31024 are high performance CMOS 1,048,576-bit Static Random Access Memory (SRAM) devices

organized as 131,072 words × 8 bits. It is designed for memory applications where fast data access, low power, and simple

interfacing are desired.

Equal address access and cycle times (t

AA

, t

RC

, t

WC

) of 10/12/15/20 ns with output enable access times (t

OE

) of 5/6/8/10 ns

are ideal for high performance applications. Active high and low chip enables (CE1, CE2) permit easy memory expansion with

multiple-bank systems.

When CE1 is high or CE2 is low the devices enter standby mode. If inputs are still toggling, the device will consume I

SB

power.

If the bus is static, then full standby power is reached (I

SB1

or I

SB2

). For example, the AS7C31024 is guaranteed not to exceed

0.33mW under nominal full standby conditions. All devices in this family will retain data when VCC is reduced as low as 2.0V.

A write cycle is accomplished by asserting write enable (WE) and both chip enables (CE1, CE2). Data on the input pins I/O0-

I/O7 is written on the rising edge of WE (write cycle 1) or the active-to-inactive edge of CE1 or CE2 (write cycle 2). To avoid

bus contention, external devices should drive I/O pins only after outputs have been disabled with output enable ( OE) or write

enable (WE).

A read cycle is accomplished by asserting output enable (OE) and both chip enables (CE1, CE2), with write enable (WE) high.

The chips drive I/O pins with the data word referenced by the input address. When either chip enable is inactive, output

enable is inactive, or write enable is active, output drivers stay in high-impedance mode.

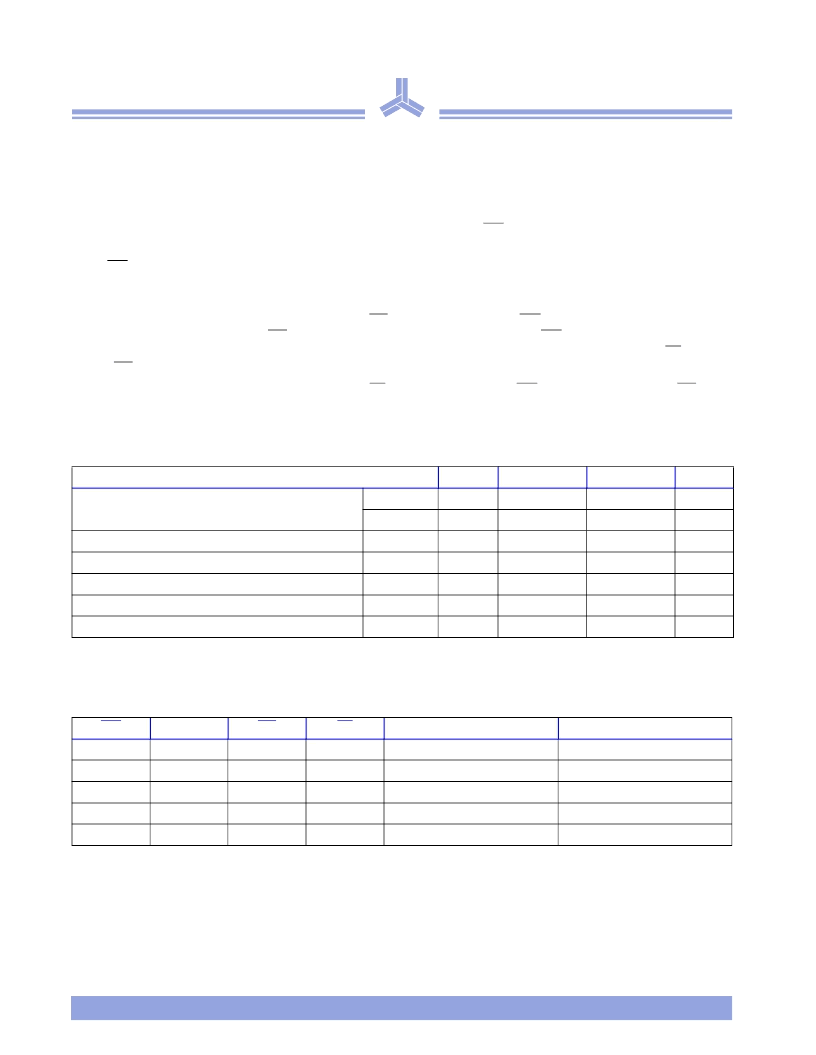

Absolute maximum ratings

Note: Stresses greater than those listed under

AbsouteMaximumRatings

may cause permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions outside those indicated in the operational sections of this specificati on is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect reliability.

Truth table

CE1

H

X

Key: X = Don’t Care, L = Low, H = High

Parameter

Symbol

V

t1

V

t1

V

t2

P

D

T

stg

T

bias

I

OUT

Min

–0.50

-0.50

–0.50

–

–65

–55

–

Max

+7.0

+5.0

Unit

V

V

V

W

°

C

°

C

mA

Voltage on V

CC

relative to GND

AS7C1024

AS7C31024

Voltage on any pin relative to GND

Power dissipation

Storage temperature (plastic)

Ambient temperature with V

CC

applied

DC current into outputs (low)

V

CC

+0.50

1.0

+150

+125

20

CE2

X

L

H

H

H

WE

X

X

H

H

L

OE

X

X

H

L

X

Data

High Z

High Z

High Z

D

OUT

D

IN

Mode

Standby (I

SB

, I

SB1

)

Standby (I

SB

, I

SB1

)

Output disable (I

CC

)

Read (I

CC

)

Write (

ICC

)

L

L

L

相关PDF资料 |

PDF描述 |

|---|---|

| AS7C31024-12TJI | 5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

| AS7C31024-15 | 5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

| AS7C31024-15JC | 5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

| AS7C31024-15JI | 5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

| AS7C31024-15TC | 5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AS7C31024-12TJI | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

| AS7C31024-12TPC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SRAM |

| AS7C31024-15 | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

| AS7C31024-15JC | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

| AS7C31024-15JI | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:5V/3.3V 128K x 8 CMOS SRAM (Evolutionary Pinout) |

发布紧急采购,3分钟左右您将得到回复。