- 您现在的位置:买卖IC网 > PDF目录209893 > ASM5P2305AF-1H-08-TT (ALLIANCE SEMICONDUCTOR CORP) 3.3V Zero Delay Buffer PDF资料下载

参数资料

| 型号: | ASM5P2305AF-1H-08-TT |

| 厂商: | ALLIANCE SEMICONDUCTOR CORP |

| 元件分类: | 时钟及定时 |

| 英文描述: | 3.3V Zero Delay Buffer |

| 中文描述: | 2305 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 封装: | 4.40 MM, TSSOP-8 |

| 文件页数: | 1/20页 |

| 文件大小: | 398K |

| 代理商: | ASM5P2305AF-1H-08-TT |

ASM5P2309A

September 2005

ASM5P2305A

rev 1.6

Alliance Semiconductor

2575 Augustine Drive

Santa Clara, CA Tel: 408.855.4900 Fax: 408.855.4999 www.alsc.com

Notice: The information in this document is subject to change without notice.

3.3V Zero Delay Buffer

General Features

15MHz to 133MHz operating range, compatible

with CPU and PCI bus frequencies.

Zero input - output propagation delay.

Multiple low-skew outputs.

Output-output skew less than 250pS.

Device-device skew less than 700pS.

One input drives 9 outputs, grouped as

4 + 4 + 1(ASM5P2309A).

One input drives 5 outputs (ASM5P2305A).

Less than 200 pS cycle-to-cycle jitter is compatible

with Pentium

based systems.

Test Mode to bypass PLL (ASM5P2309A only,

Refer Select Input Decoding Table).

Available in 16pin 150-mil SOIC, 4.4 mm TSSOP

(ASM5P2309A), and in 8pin 150-mil SOIC

package (ASM5P2305A).

3.3V operation, advanced 0.35 CMOS

technology.

Functional Description

ASM5P2309A is a versatile, 3.3V zero-delay buffer

designed to distribute high-speed clocks. It accepts one

reference input and drives out nine low-skew clocks. It is

available in a 16-pin package. The ASM5P2305A is the

eight-pin version of the ASM5P2309A. It accepts one

reference input and drives out five low-skew clocks.

The -1H version of the ASM5P23XXA operates at up to

133MHz frequencies, and has higher drive than the -1

devices. All parts have on-chip PLLs that lock to an input

clock on the REF pin. The PLL feedback is on-chip and is

obtained from the CLKOUT pad.

The ASM5P2309A has two banks of four outputs each,

which can be controlled by the Select inputs as shown in

the Select Input Decoding Table. The select input also

allows the input clock to be directly applied to the outputs

for chip and system testing purposes.

Multiple ASM5P2309A and ASM5P2305A devices can

accept the same input clock and distribute it. In this case

the skew between the outputs of the two devices is

guaranteed to be less than 700pS.

All outputs have less than 200pS of cycle-to-cycle jitter.

The input and output propagation delay is guaranteed to be

less than 350pS, and the output to output skew is

guaranteed to be less than 250pS.

The ASM5P2309A and the ASM5P2305A are available in

two different configurations, as shown in the ordering

information table. The ASM5P2305A-1/ ASM5P2309A-1 is

the base part. The ASM5P2305A-1H/ ASM5P2309A-1H is

the high drive version of the -1 and its rise and fall times

are much faster than -1 part.

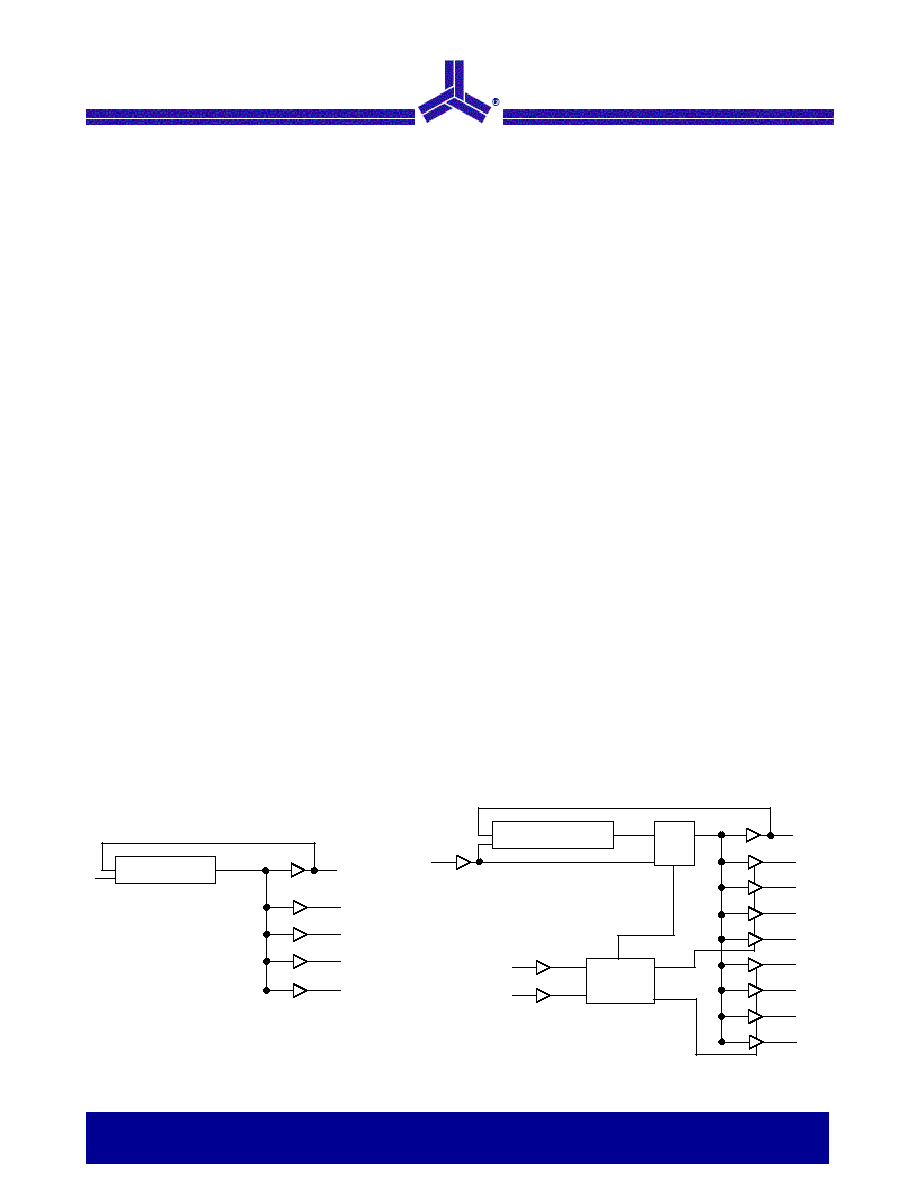

Block Diagram

ASM5P2309A

PLL

MUX

CLKOUT

CLKA1

CLKA2

CLKA3

CLKA4

CLKB1

CLKB2

CLKB3

CLKB4

Select Input

Decoding

S2

S1

REF

PLL

CLKOUT

CLK1

CLK2

CLK3

CLK4

ASM5P2305A

REF

相关PDF资料 |

PDF描述 |

|---|---|

| ASM5P2309AG-1H-16-TT | LM4121 Precision Micropower Low Dropout Voltage Reference; Package: SOT-23; No of Pins: 5 |

| A381414L1 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| A381415L6 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| A38102L3 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| A381103L4 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ASM5P2305AG-1-08-SR | 制造商:PULSECORE 制造商全称:PulseCore Semiconductor 功能描述:3.3V Zero Delay Buffer |

| ASM5P2305AG-1-08-ST | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:3.3V Zero Delay Buffer |

| ASM5P2305AG-1-08-TR | 制造商:PULSECORE 制造商全称:PulseCore Semiconductor 功能描述:3.3V Zero Delay Buffer |

| ASM5P2305AG-1-08-TT | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:3.3V Zero Delay Buffer |

| ASM5P2305AG-1H-08-SR | 制造商:PULSECORE 制造商全称:PulseCore Semiconductor 功能描述:3.3V Zero Delay Buffer |

发布紧急采购,3分钟左右您将得到回复。