- 您现在的位置:买卖IC网 > PDF目录19914 > AT17LV512A-10PU (Atmel)IC FPGA EEPROM 512K ALTERA 8PDIP PDF资料下载

参数资料

| 型号: | AT17LV512A-10PU |

| 厂商: | Atmel |

| 文件页数: | 13/18页 |

| 文件大小: | 0K |

| 描述: | IC FPGA EEPROM 512K ALTERA 8PDIP |

| 标准包装: | 50 |

| 可编程类型: | 串行 EEPROM |

| 存储容量: | 512kb |

| 电源电压: | 3 V ~ 3.6 V,4.5 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-DIP(0.300",7.62mm) |

| 供应商设备封装: | 8-DIP |

| 包装: | 管件 |

| 配用: | ATDH2225-ND - CABLE ISP FOR AT17 ATDH2200E-ND - CONFIGURATOR PROGRAM BOARD KIT |

4

2322G–CNFG–03/06

AT17LV65A/128A/256A/512A/002A

3.

Device Description

The control signals for the configuration EEPROM (nCS, RESET/OE and DCLK) interface

directly with the FPGA device control signals. All FPGA devices can control the entire configura-

tion process and retrieve data from the configuration EEPROM without requiring an external

controller.

The configuration EEPROM’s RESET/OE and nCS pins control the tri-state buffer on the DATA

output pin and enable the address counter and the oscillator. When RESET/OE is driven Low,

the configuration EEPROM resets its address counter and tri-states its DATA pin. The nCS pin

also controls the output of the AT17A series configurator. If nCS is held High after the

RESET/OE pulse, the counter is disabled and the DATA output pin is tri-stated. When nCS is

driven subsequently Low, the counter and the DATA output pin are enabled. When RESET/OE

is driven Low again, the address counter is reset and the DATA output pin is tri-stated, regard-

less of the state of the nCS.

When the configurator has driven out all of its data and nCASC is driven Low, the device tri-

states the DATA pin to avoid contention with other configurators. Upon power-up, the address

counter is automatically reset.

This is the default setting for the device. Since almost all FPGAs use RESET Low and OE High,

this document will describe RESET/OE.

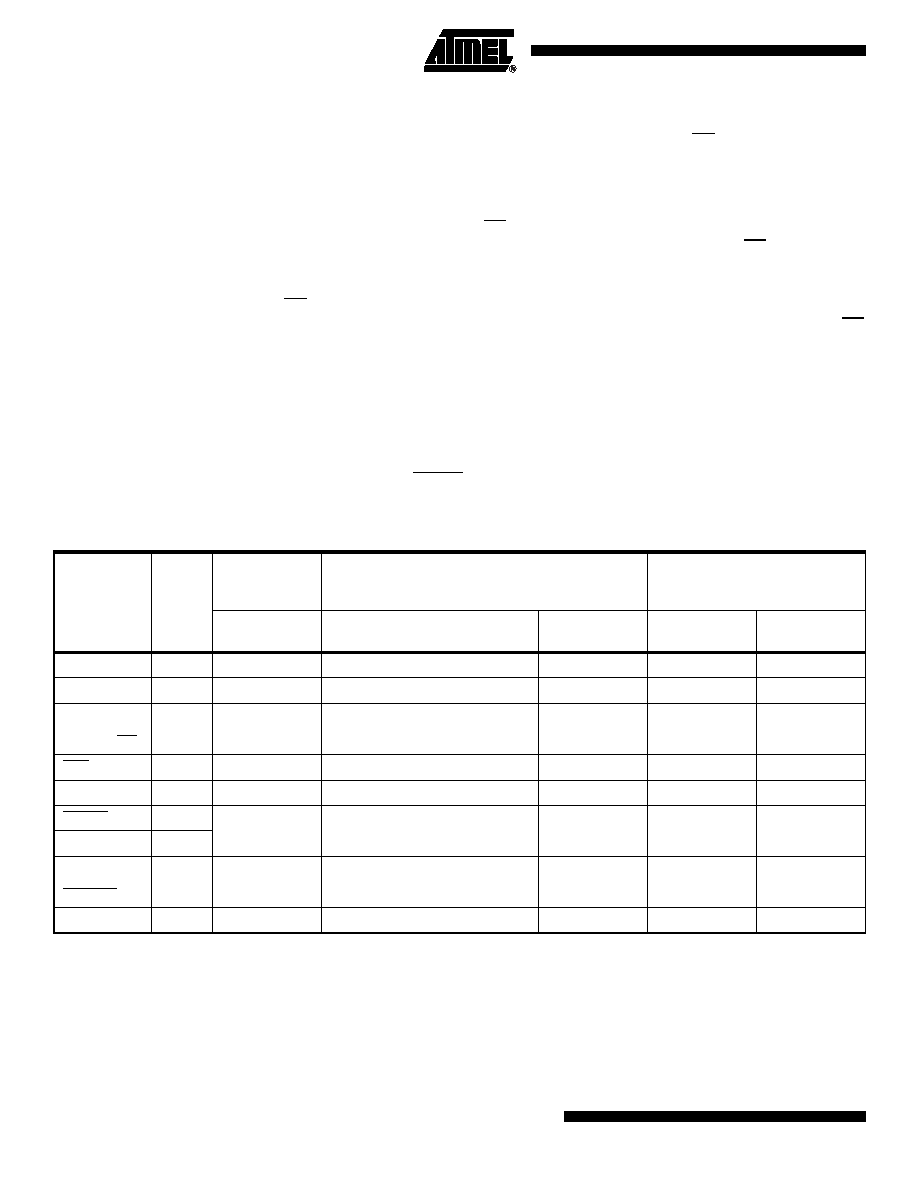

4.

Pin Description

Note:

1. The nCASC feature is not available on the AT17LV65A device.

Name

I/O

AT17LV65A/

AT17LV128A/

AT17LV256A

AT17LV512A/

AT17LV010A

AT17LV002A

20

PLCC

8

PDIP

20

PLCC

32

TQFP

20

PLCC

32

TQFP

DATA

I/O

2

1

2

31

2

31

DCLK

I

42

4242

WP1

I

––

5454

RESET/OE

I

8

3

8787

nCS

I9

4

9

10

9

10

GND

10

5

10

12

10

12

nCASC

O

12

6

12151215

A2

I

READY

O

–

15

20

15

20

SER_EN

I

18

7

18

23

18

23

V

CC

20

8

20272027

相关PDF资料 |

PDF描述 |

|---|---|

| GRM1885C1H242JA01D | CAP CER 2400PF 50V 5% NP0 0603 |

| T95R336M035EZAS | CAP TANT 33UF 35V 20% 2824 |

| 1250F7 | BATTERY PK S-HD 10.5V DSIZE ZINC |

| NCV8503PWADJR2G | IC REG LDO ADJ .4A 16SOIC |

| VE-JNK-CY-B1 | CONVERTER MOD DC/DC 40V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT17LV512A-10SC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

| AT17LV512A-10SI | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

| AT17LV512A-10TQC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

| AT17LV512A-10TQI | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:FPGA Configuration EEPROM Memory |

| AT17LV512-W | 功能描述:FPGA-配置存储器 FPGA CONFIG SERIAL EEPROM, 512K, ALTERA PINOUT - DIE WAFER RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

发布紧急采购,3分钟左右您将得到回复。