参数资料

| 型号: | AT90S8515A-8PC |

| 厂商: | Atmel |

| 文件页数: | 59/112页 |

| 文件大小: | 0K |

| 描述: | IC MCU 8K FLSH 8MHZ 40DIP |

| 标准包装: | 18 |

| 系列: | AVR® 90S |

| 核心处理器: | AVR |

| 芯体尺寸: | 8-位 |

| 速度: | 8MHz |

| 连通性: | SPI,UART/USART |

| 外围设备: | 欠压检测/复位,POR,PWM,WDT |

| 输入/输出数: | 32 |

| 程序存储器容量: | 8KB(4K x 16) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 512 x 8 |

| RAM 容量: | 512 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 4 V ~ 6 V |

| 振荡器型: | 内部 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页

50

AT90S8515

0841G–09/01

Bit 5 – DORD: Data Order

When the DORD bit is set (one), the LSB of the data word is transmitted first.

When the DORD bit is cleared (zero), the MSB of the data word is transmitted first.

Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI Mode when set (one), and Slave SPI Mode when cleared

(zero). If SS is configured as an input and is driven low while MSTR is set, MSTR will be

cleared and SPIF in SPSR will become set. The user will then have to set MSTR to re-

enable SPI Master Mode.

Bit 3 – CPOL: Clock Polarity

When this bit is set (one), SCK is high when idle. When CPOL is cleared (zero), SCK is

Bit 2 – CPHA: Clock Phase

Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a master. SPR1 and

SPR0 have no effect on the slave. The relationship between SCK and the oscillator

SPI Status Register – SPSR

Bit 7 – SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF bit is set (one) and an interrupt is gener-

ated if SPIE in SPCR is set (one) and global interrupts are enabled. If SS is an input and

is driven low when the SPI is in Master Mode, this will also set the SPIF flag. SPIF is

cleared by hardware when executing the corresponding interrupt handling vector. Alter-

natively, the SPIF bit is cleared by first reading the SPI Status Register when SPIF is set

(one), then by accessing the SPI Data Register (SPDR).

Bit 6 – WCOL: Write Collision Flag

The WCOL bit is set if the SPI Data Register (SPDR) is written during a data transfer.

The WCOL bit (and the SPIF bit) are cleared (zero) by first reading the SPI Status Reg-

ister when WCOL is set (one), and then by accessing the SPI Data Register.

Bits 5..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and will always read as zero.

The SPI interface on the AT90S8515 is also used for program memory and EEPROM

downloading or uploading. See page 86 for serial programming and verification.

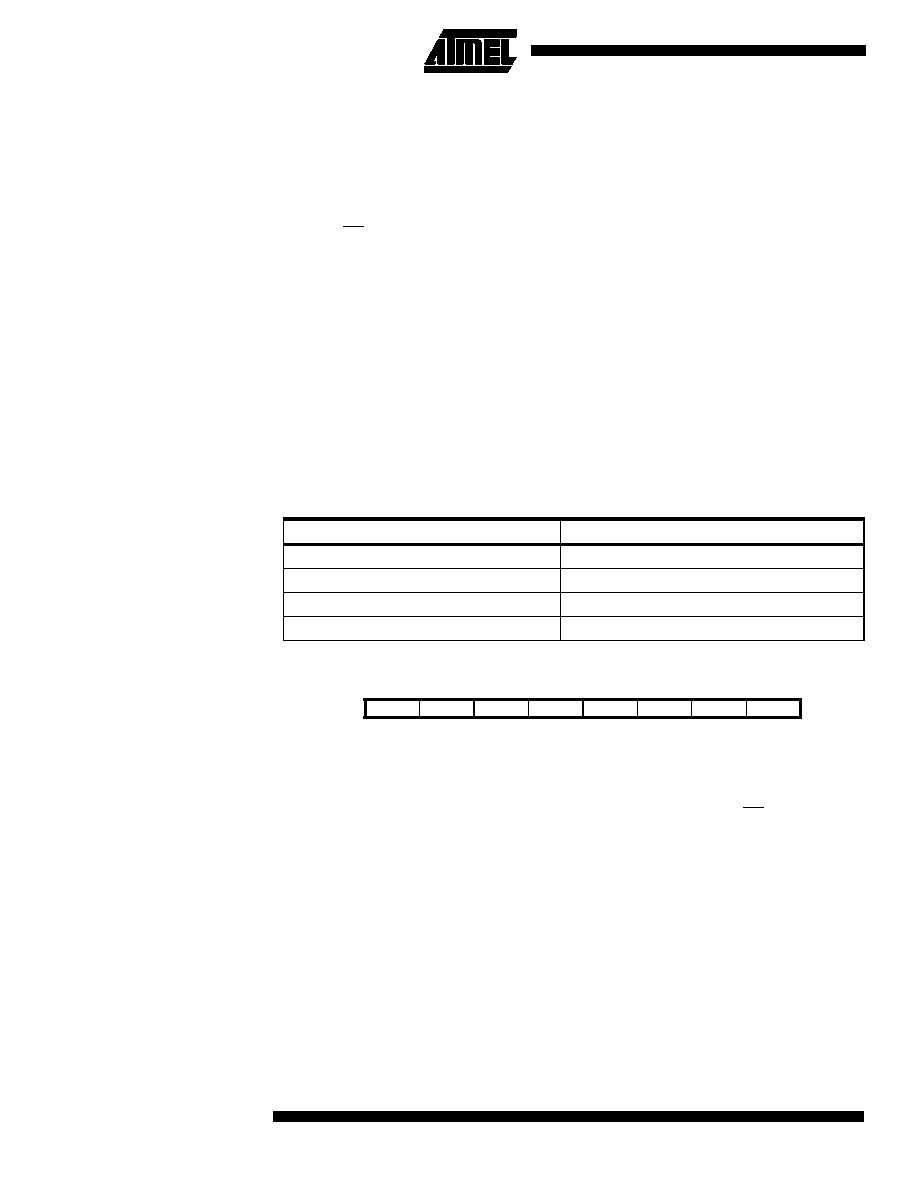

Table 16. Relationship between SCK and the Oscillator Frequency

SPR1

SPR0

SCK Frequency

00

f

cl/4

01

f

cl/16

10

fcl/64

11

f

cl/128

Bit

765

432

10

$0E ($2E)

SPIF

WCOL

–

SPSR

Read/Write

RR

RRR

Initial Value

0

相关PDF资料 |

PDF描述 |

|---|---|

| AT90S8535-8PI | IC MCU 8K FLSH 8MHZ A/D IT 40DIP |

| AT90USB1287-16AUR | IC MCU AVR 128K ISP USB TQFP64 |

| AT90USB162-16AUR | IC AVR MCU 16K FLASH 32TQFP |

| AT91FR40162SB-CU-999 | IC MCU 32BIT RISC 121BGA |

| AT91M40800-33AI SL383 | IC ARM MCU 16BIT 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT90S8515A-8PI | 功能描述:IC MCU 8BIT 8KB FLASH 40DIP 制造商:microchip technology 系列:AVR? 90S 包装:管件 零件状态:停產 核心处理器:AVR 核心尺寸:8-位 速度:8MHz 连接性:SPI,UART/USART 外设:欠压检测/复位,POR,PWM,WDT I/O 数:32 程序存储容量:8KB(4K x 16) 程序存储器类型:闪存 EEPROM 容量:512 x 8 RAM 容量:512 x 8 电压 - 电源(Vcc/Vdd):4 V ~ 6 V 数据转换器:- 振荡器类型:内部 工作温度:-40°C ~ 85°C 封装/外壳:40-DIP(0.600",15.24mm) 供应商器件封装:40-PDIP 基本零件编号:AT90S8515 标准包装:18 |

| AT90S8515-JC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| AT90S8515-JI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| AT90S8515-PC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| AT90S8515-PI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。