- 您现在的位置:买卖IC网 > PDF目录19654 > ATF1500A-10JI (Atmel)IC CPLD 10NS 44PLCC PDF资料下载

参数资料

| 型号: | ATF1500A-10JI |

| 厂商: | Atmel |

| 文件页数: | 3/19页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 10NS 44PLCC |

| 标准包装: | 27 |

| 系列: | ATF15xx |

| 可编程类型: | 系统内可编程(最少 100 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 10.0ns |

| 电压电源 - 内部: | 4.5 V ~ 5.5 V |

| 宏单元数: | 32 |

| 输入/输出数: | 32 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC |

| 包装: | 管件 |

| 其它名称: | ATF1500A10JI |

ATF1500A(L)

11

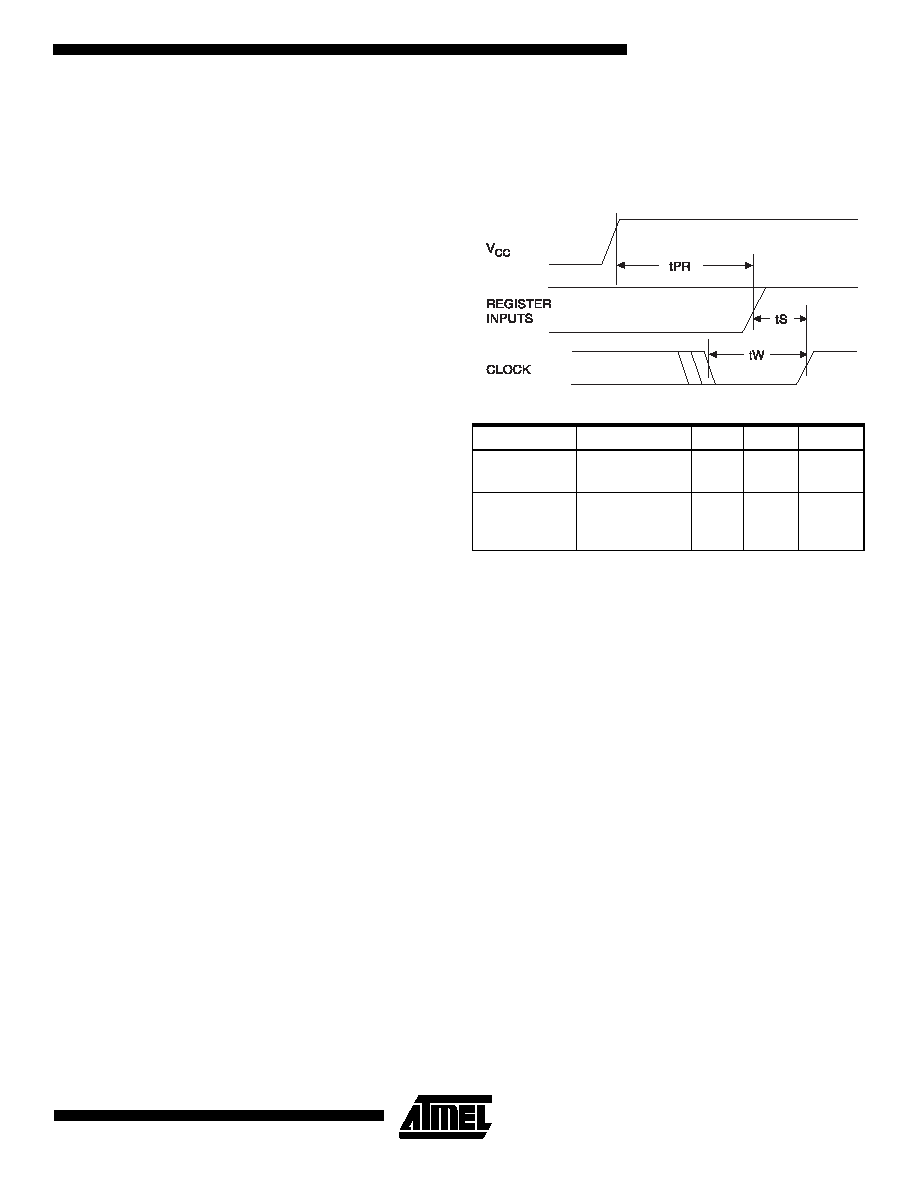

Power-up Reset

The ATF1500A’s registers are designed to reset during

power-up. At a point delayed slightly from V

CC crossing

V

RST, all registers will be reset to the low state. As a result,

the registered output state will always be low on power-up.

This feature is critical for state machine initialization. How-

ever, due to the asynchronous nature of reset and the

uncertainty of how V

CC actually rises in the system, the fol-

lowing conditions are required:

1. The V

CC rise must be monotonic, from below 0.7 volt,

2. After reset occurs, all input and feedback setup times

must be met before driving the clock signal high, and

3. Signals from which clocks are derived must remain sta-

ble during t

PR.

Power-down Mode

The ATF1500A includes an optional pin-controlled power-

down feature. When this mode is enabled, the PD pin acts

as the power down pin. When the PD pin is high, the device

supply current is reduced to less than 10 mA. During

power-down, all output data and internal logic states are

latched and held. Therefore, all registered and combinato-

rial output data remain valid. Any outputs that were in a

high-Z state at the onset of power-down will remain at

high-Z. During power-down, all input signals except the

power-down pin are blocked. Input and I/O hold latches

remain active to ensure that pins do not float to indetermi-

nate levels, further reducing system power. The power-

down pin feature is enabled in the logic design file. Designs

using the power-down pin may not use the PD pin logic

array input. However, all other PD pin macrocell resources

may still be used, including the buried feedback and fold-

back product term array inputs.

Register Preload

The ATF1500A’s registers are provided with circuitry to

allow loading of each register with either a high or a low.

This feature will simplify testing since any state can be

forced into the registers to control test sequencing. A

JEDEC file with preload is generated when a source file

with preload vectors is compiled. Once downloaded, the

JEDEC file preload sequence will be done automatically

when vectors are run by any approved programmers. The

preload mode is enabled by raising an input pin to a high

voltage level. Contact Atmel PLD Applications for PRE-

LOAD pin assignments, timing and voltage requirements.

Output Slew Rate Control

Each ATF1500A macrocell contains a configuration bit for

each I/O to control its output slew rate. This allows selected

data paths to operate at maximum throughput while reduc-

ing system noise from outputs that are not speed-critical.

Outputs default to slow edges, and may be individually set

to fast in the design file. Output transition times for outputs

configured as “slow” have a t

SSO delay adder.

Security Fuse Usage

A single fuse is provided to prevent unauthorized copying

of the ATF1500A fuse patterns. Once programmed, fuse

verify and preload are prohibited. However, the 160-bit

User Signature remains accessible.

The security fuse should be programmed last, as its effect

is immediate.

Parameter

Description

Typ

Max

Units

tPR

Power-up

Reset Time

210

s

VRST

Power-up

Reset

Voltage

3.8

4.5

V

相关PDF资料 |

PDF描述 |

|---|---|

| EMA49DTBD | CONN EDGECARD 98POS R/A .125 SLD |

| ATF1500A-10AI | IC CPLD 10NS 44TQFP |

| EBC10DCSD | CONN EDGECARD 20POS DIP .100 SLD |

| M4A3-512/192-10FANI | IC CPLD ISP 4A 512MC 256FPBGA |

| ATF750CL-15SC | IC CPLD 15NS LOW PWR 24-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATF1500A-10JU | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL CMPTBLE w/F1500 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1500A-12AC | 功能描述:IC CPLD 12NS 44TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:ATF15xx 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| ATF1500A-12AI | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Highperformance EPLD |

| ATF1500A-12JC | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL CMPTBLE w/F1500 5V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1500A-12JI | 功能描述:CPLD - 复杂可编程逻辑器件 ASICS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。