- 您现在的位置:买卖IC网 > PDF目录19659 > ATF1504ASVL-20AC100 (Atmel)IC CPLD 64MACROCEL LV LP 100TQFP PDF资料下载

参数资料

| 型号: | ATF1504ASVL-20AC100 |

| 厂商: | Atmel |

| 文件页数: | 30/31页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 64MACROCEL LV LP 100TQFP |

| 标准包装: | 90 |

| 系列: | ATF15xx |

| 可编程类型: | 系统内可编程(最少 10,000 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 20.0ns |

| 电压电源 - 内部: | 3 V ~ 3.6 V |

| 宏单元数: | 64 |

| 输入/输出数: | 64 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | ATF1504ASVL20AC10 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页

8

ATF1504ASV(L)

1409J–PLD–6/05

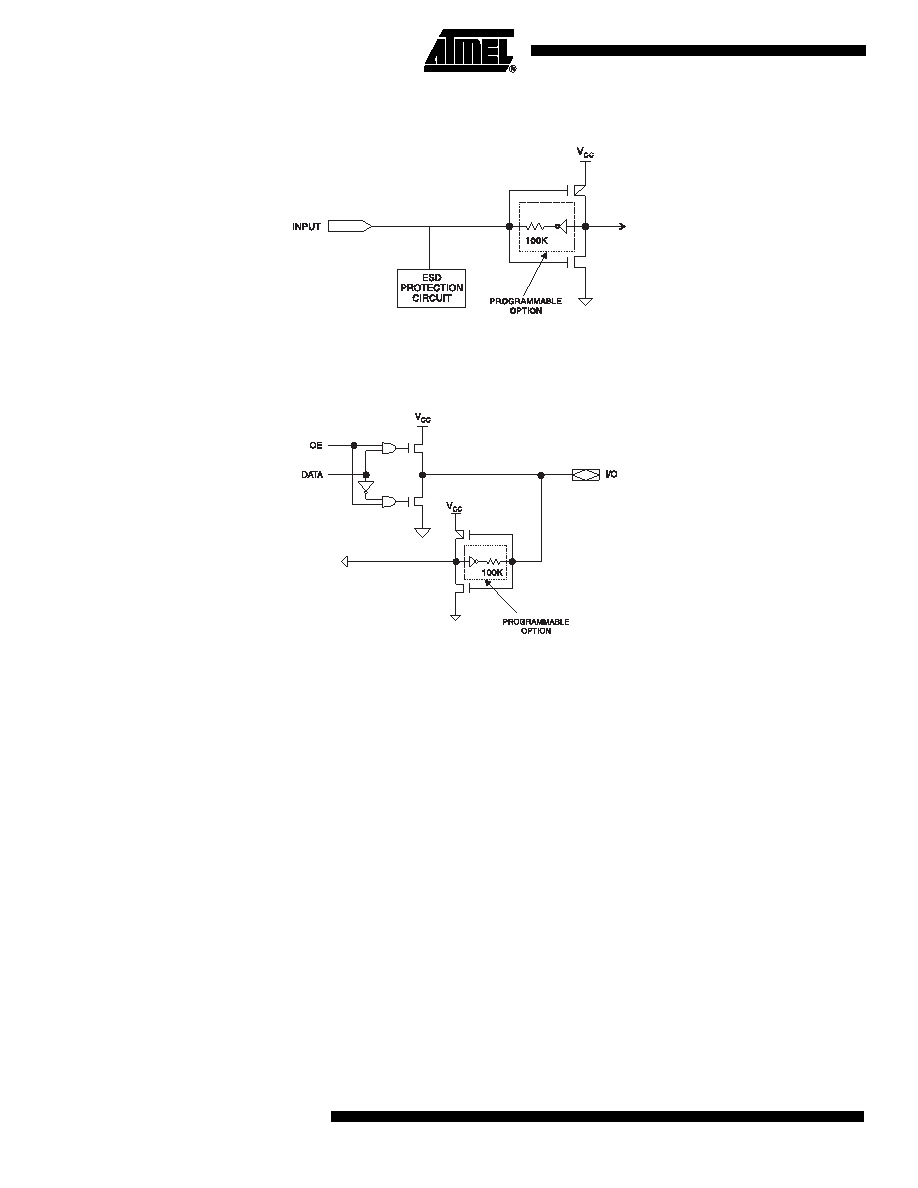

Input Diagram

I/O Diagram

Speed/Power

Management

The ATF1504ASV(L) has several built-in speed and power management features. The

ATF1504ASV(L) contains circuitry that automatically puts the device into a low power

standby mode when no logic transitions are occurring. This not only reduces power con-

sumption during inactive periods, but also provides proportional power savings for most

applications running at system speeds below 5 MHz. This feature may be selected as a

device option.

To further reduce power, each ATF1504ASV(L) macrocell has a reduced-power bit fea-

ture. This feature allows individual macrocells to be configured for maximum power

savings. This feature may be selected as a design option.

All ATF1504ASV(L) also have an optional power-down mode. In this mode, current

drops to below 5 mA. When the power-down option is selected, either PD1 or PD2 pins

(or both) can be used to power down the part. The power-down option is selected in the

design source file. When enabled, the device goes into power down when either PD1 or

PD2 is high. In the power-down mode, all internal logic signals are latched and held, as

are any enabled outputs.

All pin transitions are ignored until the PD pin is brought low. When the power-down fea-

ture is enabled, the PD1 or PD2 pin cannot be used as a logic input or output. However,

the pin’s macrocell may still be used to generate buried foldback and cascade logic

signals.

相关PDF资料 |

PDF描述 |

|---|---|

| NCP1216AP133G | IC CTRLR PWM CM OTP HV 8DIP |

| TAJT225M025RNJ | CAP TANT 2.2UF 25V 20% 1210 |

| VE-B0N-CY-F3 | CONVERTER MOD DC/DC 18.5V 50W |

| VE-B0L-CY-F1 | CONVERTER MOD DC/DC 28V 50W |

| NCP1217P100G | IC CTRLR PWM CM OVP HV 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATF1504ASVL-20AC44 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 64 MACROCELL w/ISP LOW PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20AI100 | 功能描述:CPLD - 复杂可编程逻辑器件 64 MACROCELL w/ISP LO-PWR 3.3V-20NS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20AI44 | 功能描述:CPLD - 复杂可编程逻辑器件 64 Macrocell RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20AU100 | 功能描述:CPLD - 复杂可编程逻辑器件 64 MACROCELL w/ISP LO-PWR 3.3V-20NS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20AU44 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 64 MACROCELL w/ISP LOW PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。