- 您现在的位置:买卖IC网 > PDF目录19656 > ATF1504ASVL-20AC44 (Atmel)IC CPLD 64MACROCELL LV LP 44TQFP PDF资料下载

参数资料

| 型号: | ATF1504ASVL-20AC44 |

| 厂商: | Atmel |

| 文件页数: | 7/31页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 64MACROCELL LV LP 44TQFP |

| 标准包装: | 160 |

| 系列: | ATF15xx |

| 可编程类型: | 系统内可编程(最少 10,000 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 20.0ns |

| 电压电源 - 内部: | 3 V ~ 3.6 V |

| 宏单元数: | 64 |

| 输入/输出数: | 32 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-TQFP |

| 供应商设备封装: | 44-TQFP(10x10) |

| 包装: | 托盘 |

| 其它名称: | ATF1504ASVL20AC44 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

15

ATF1504ASV(L)

1409J–PLD–6/05

Power-down Mode

The ATF1504ASV(L) includes an optional pin-controlled power-down feature. When this

mode is enabled, the PD pin acts as the power-down pin. When the PD pin is high, the

device supply current is reduced to less than 3 mA. During power down, all output data

and internal logic states are latched internally and held. Therefore, all registered and

combinatorial output data remain valid. Any outputs that were in a High-Z state at the

onset will remain at High-Z. During power down, all input signals except the power-down

pin are blocked. Input and I/O hold latches remain active to ensure that pins do not float

to indeterminate levels, further reducing system power. The power-down mode feature

is enabled in the logic design file or as a fitted or translated s/w option. Designs using

the power-down pin may not use the PD pin as a logic array input. However, all other PD

pin macrocell resources may still be used, including the buried feedback and foldback

product term array inputs.

Notes:

1. For slow slew outputs, add t

SSO.

2. Pin or product term.

3. Includes t

RPA for reduced-power bit enabled.

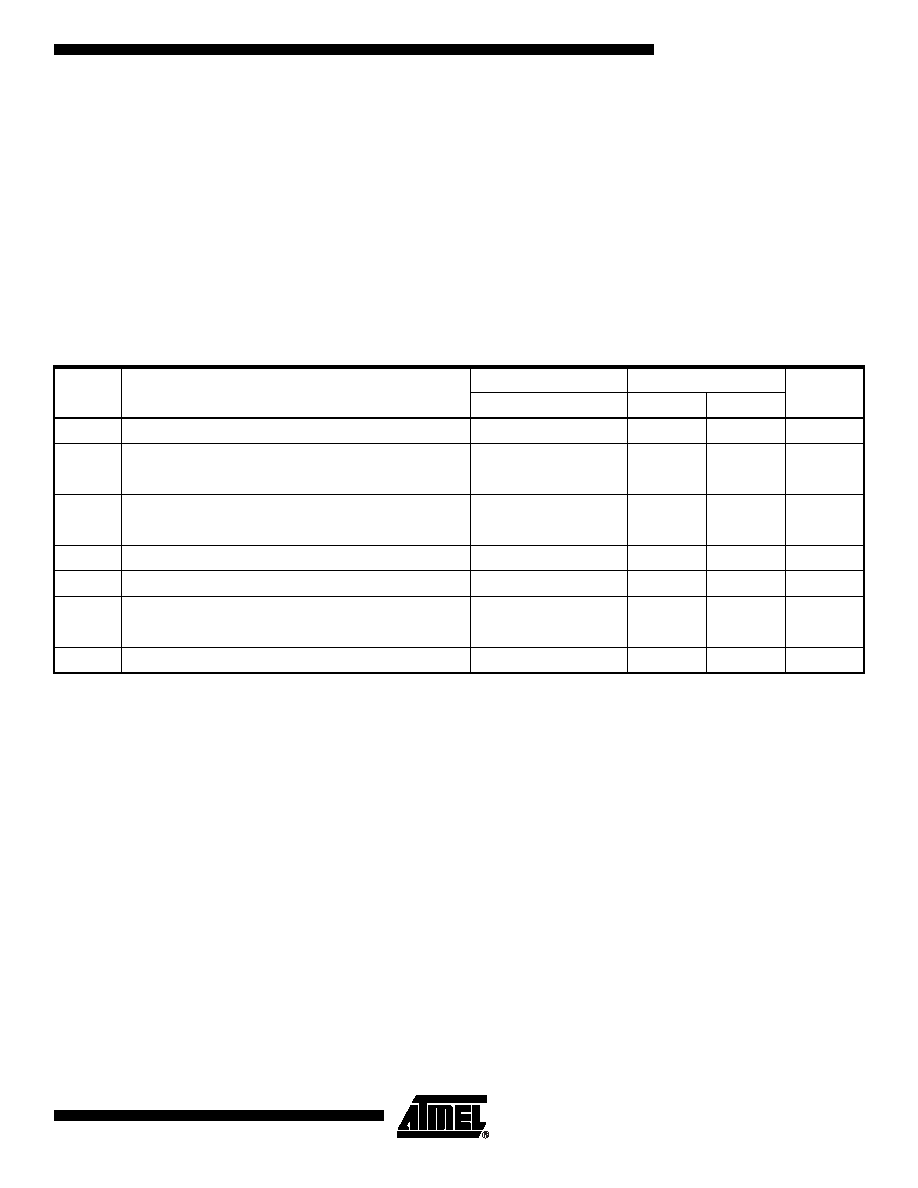

Power Down AC Characteristics

Symbol

Parameter

-15

-20

Units

Min

Max

Min

Max

t

IVDH

Valid I, I/O before PD High

15

20

ns

tGVDH

Valid OE(2) before PD High

15

20

ns

t

CVDH

Valid Clock(2) before PD High

15

20

ns

t

DHIX

I, I/O Don’t Care after PD High

25

30

ns

tDHGX

OE(2) Don’t Care after PD High

25

30

ns

t

DHCX

Clock(2) Don’t Care after PD High

25

30

ns

t

DLIV

PD Low to Valid I, I/O

1

s

tDLGV

PD Low to Valid OE (Pin or Term)

1

s

t

DLCV

PD Low to Valid Clock (Pin or Term)

1

s

t

DLOV

PD Low to Valid Output

1

s

相关PDF资料 |

PDF描述 |

|---|---|

| GBM06DRSN | CONN EDGECARD 12POS DIP .156 SLD |

| ATF1508AS-10JC84 | IC CPLD 128 MACROCELL 84PLCC |

| DE2B3KY471KA2BM01 | CAP CER 470PF 250V 10% RADIAL |

| GBM06DRSH | CONN EDGECARD 12POS DIP .156 SLD |

| LC51024MV-75FN484C | IC CPLD 1024MACROCELLS 484FPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATF1504ASVL-20AI100 | 功能描述:CPLD - 复杂可编程逻辑器件 64 MACROCELL w/ISP LO-PWR 3.3V-20NS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20AI44 | 功能描述:CPLD - 复杂可编程逻辑器件 64 Macrocell RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20AU100 | 功能描述:CPLD - 复杂可编程逻辑器件 64 MACROCELL w/ISP LO-PWR 3.3V-20NS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20AU44 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 64 MACROCELL w/ISP LOW PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1504ASVL-20JC44 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 64 MACROCELL w/ISP LOW PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。