参数资料

| 型号: | ATTINY48-AUR |

| 厂商: | Atmel |

| 文件页数: | 21/302页 |

| 文件大小: | 0K |

| 描述: | MCU AVR 4KB FLASH 12MHZ 32TQFP |

| 产品培训模块: | tinyAVR Introduction |

| 标准包装: | 2,000 |

| 系列: | AVR® ATtiny |

| 核心处理器: | AVR |

| 芯体尺寸: | 8-位 |

| 速度: | 12MHz |

| 连通性: | I²C,SPI |

| 外围设备: | 欠压检测/复位,POR,WDT |

| 输入/输出数: | 28 |

| 程序存储器容量: | 4KB(2K x 16) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 64 x 8 |

| RAM 容量: | 256 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 1.8 V ~ 5.5 V |

| 数据转换器: | A/D 8x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 32-TQFP |

| 包装: | 带卷 (TR) |

| 其它名称: | ATTINY48-AUR-ND ATTINY48-AURTR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页第229页第230页第231页第232页第233页第234页第235页第236页第237页第238页第239页第240页第241页第242页第243页第244页第245页第246页第247页第248页第249页第250页第251页第252页第253页第254页第255页第256页第257页第258页第259页第260页第261页第262页第263页第264页第265页第266页第267页第268页第269页第270页第271页第272页第273页第274页第275页第276页第277页第278页第279页第280页第281页第282页第283页第284页第285页第286页第287页第288页第289页第290页第291页第292页第293页第294页第295页第296页第297页第298页第299页第300页第301页第302页

117

8008H–AVR–04/11

ATtiny48/88

13. Timer/Counter0 and Timer/Counter1 Prescalers

same prescaler module, but the Timer/Counters can have different prescaler settings. The

description below applies to both Timer/Counter1 and Timer/Counter0.

13.1

Internal Clock Source

The Timer/Counter can be clocked directly by the system clock (by setting the CSn[2:0] = 1).

This provides the fastest operation, with a maximum Timer/Counter clock frequency equal to

system clock frequency (f

CLK_I/O). Alternatively, one of four taps from the prescaler can be used

as a clock source. The prescaled clock has a frequency of either f

CLK_I/O/8, fCLK_I/O/64,

f

CLK_I/O/256, or fCLK_I/O/1024.

13.2

Prescaler Reset

The prescaler is free running, i.e., operates independently of the Clock Select logic of the

Timer/Counter, and it is shared by Timer/Counter1 and Timer/Counter0. Since the prescaler is

not affected by the Timer/Counter’s clock select, the state of the prescaler will have implications

for situations where a prescaled clock is used. One example of prescaling artifacts occurs when

the timer is enabled and clocked by the prescaler (CSn[2:0] = 0b010, 0b011, 0b100, or 0b101).

The number of system clock cycles from when the timer is enabled to the first count occurs can

be from 1 to N+1 system clock cycles, where N equals the prescaler divisor (8, 64, 256, or

1024).

It is possible to use the prescaler reset for synchronizing the Timer/Counter to program execu-

tion. However, care must be taken if the other Timer/Counter that shares the same prescaler

also uses prescaling. A prescaler reset will affect the prescaler period for all Timer/Counters it is

connected to.

13.3

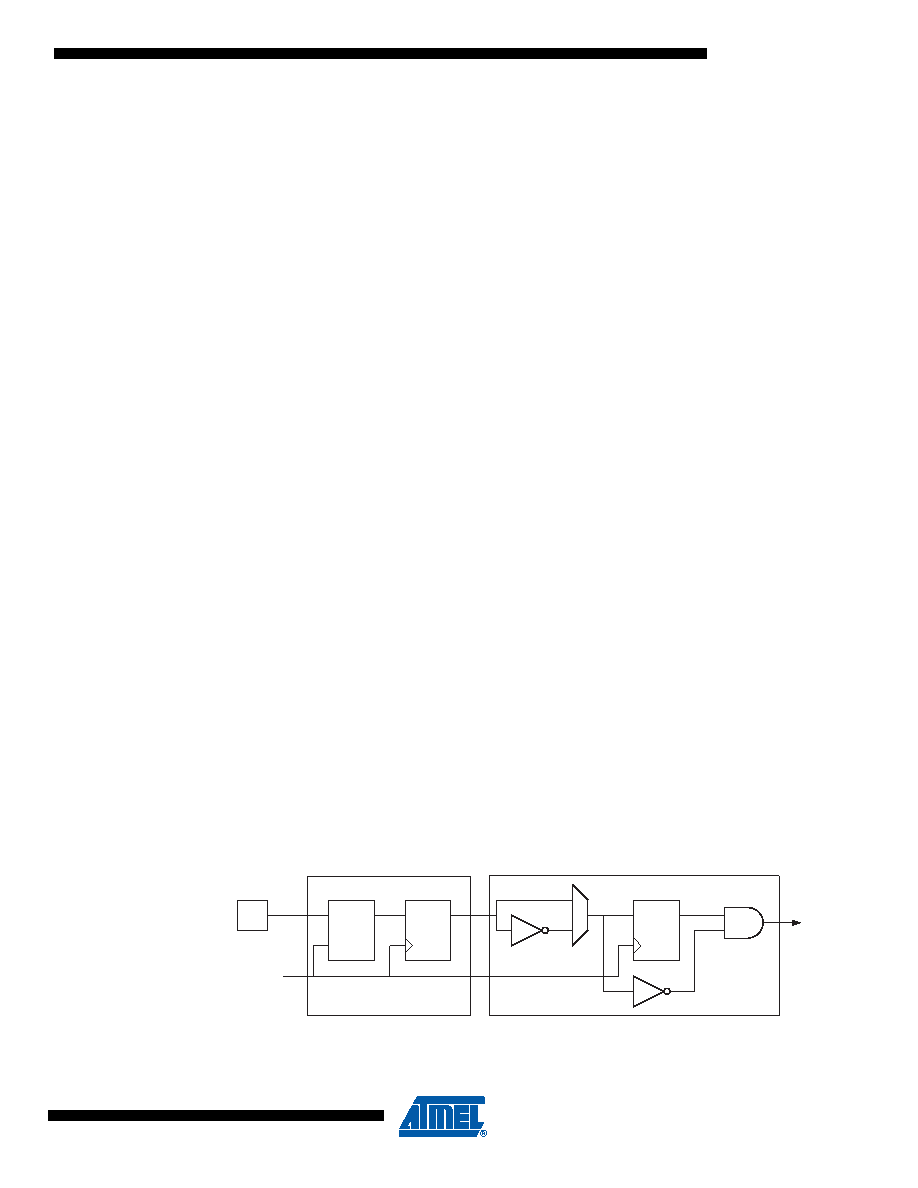

External Clock Source

An external clock source applied to the T1/T0 pin can be used as Timer/Counter clock

(clk

T1/clkT0). The T1/T0 pin is sampled once every system clock cycle by the pin synchronization

logic. The synchronized (sampled) signal is then passed through the edge detector. Figure 13-1

shows a functional equivalent block diagram of the T1/T0 synchronization and edge detector

logic. The registers are clocked at the positive edge of the internal system clock (clk

I/O). The latch

is transparent in the high period of the internal system clock.

The edge detector generates one clk

T1/clkT0 pulse for each positive (CSn[2:0] = 7) or negative

(CSn[2:0] = 6) edge it detects.

Figure 13-1. T1/T0 Pin Sampling

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles

from an edge has been applied to the T1/T0 pin to the counter is updated.

Tn_sync

(To Clock

Select Logic)

Edge Detector

Synchronization

DQ

LE

DQ

Tn

clk

I/O

相关PDF资料 |

PDF描述 |

|---|---|

| ATTINY48-MMUR | MCU AVR 4KB FLASH 12MHZ 28MLF |

| ATTINY84A-MMHR | MCU AVR 8K FLASH 20MHZ 3X3VQFN |

| ATTINY84V-10SSUR | MCU AVR 8KB FLASH 10MHZ 14SOIC |

| ATTINY84V-10SSU | MCU AVR 8K ISP FLASH 1.8V 14SOIC |

| ATTINY861-15SZ | MCU AVR 8K FLASH 15MHZ 20-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATTINY48-CCU | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 4/8K Bytes In-System Programmable Flash |

| ATTINY48-CCUR | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 4/8K Bytes In-System Programmable Flash |

| ATTINY48-MMH | 功能描述:8位微控制器 -MCU AVR 4KB, 64B EE 12MHz 256B SRAM, 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ATTINY48-MMHR | 功能描述:8位微控制器 -MCU AVR 4KB FLSH 64B EE 256B 12MHz NiPdAu RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ATTINY48-MMU | 功能描述:8位微控制器 -MCU 4KB In-system Flash 12MHz 1.8V-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。