- 您现在的位置:买卖IC网 > PDF目录295169 > BS62LV2006TIP55 (BRILLIANCE SEMICONDUCTOR, INC.) Very Low Power/Voltage CMOS SRAM 256K X 8 bit PDF资料下载

参数资料

| 型号: | BS62LV2006TIP55 |

| 厂商: | BRILLIANCE SEMICONDUCTOR, INC. |

| 英文描述: | Very Low Power/Voltage CMOS SRAM 256K X 8 bit |

| 中文描述: | 非常低功率/电压CMOS SRAM的256K × 8位 |

| 文件页数: | 3/9页 |

| 文件大小: | 321K |

| 代理商: | BS62LV2006TIP55 |

R0201-BS62LV2006

Revision 1.1

Jan.

2004

3

BSI

SYMBOL

PARAMETER

TEST CONDITIONS

MIN.

TYP. (1)

MAX.

UNITS

VDR

Vcc for Data Retention

CE1 ≧ Vcc - 0.2V or CE2 ≦ 0.2V,

VIN ≧ Vcc - 0.2V or VIN ≦ 0.2V

1.5

--

V

ICCDR

(3)

Data Retention Current

CE1 ≧ Vcc - 0.2V or CE2 ≦ 0.2V,

VIN ≧ Vcc - 0.2V or VIN ≦ 0.2V

--

0.1

1.0

uA

tCDR

Chip Deselect to Data

Retention Time

0

--

ns

tR

Operation Recovery Time

See Retention Waveform

TRC

(2)

--

ns

1. Typical characteristics are at TA = 25oC.

2. Fmax = 1/t

RC .

3. These are absolute values with respect to device ground and all overshoots due to system or tester notice are included.

4. IccsB1_MAX. is 3uA/ 10uA at Vcc=3V/ 5V and TA=70oC.

5. Icc_MAX. is 23mA(@3V)/ 55mA(@5V) under 55ns operation.

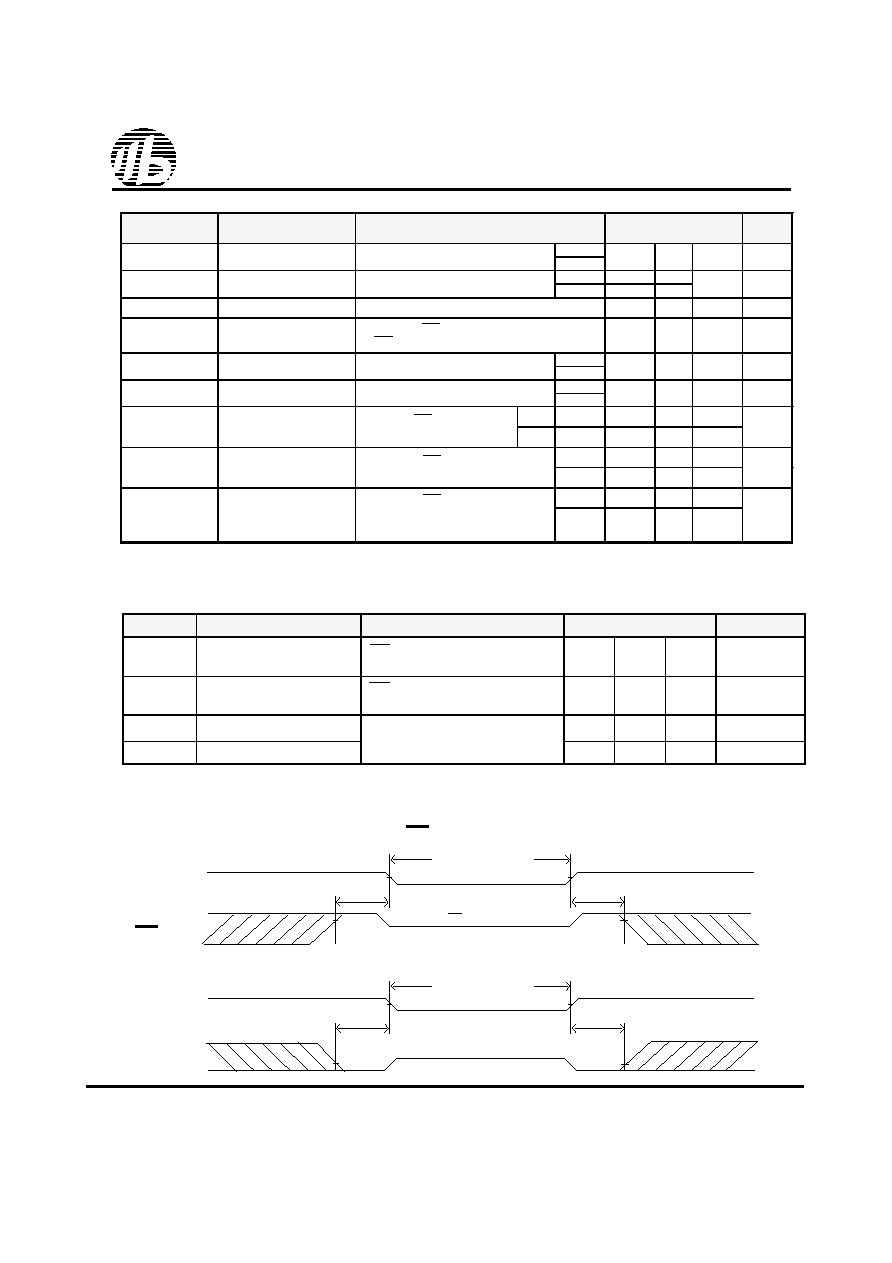

DATA RETENTION CHARACTERISTICS ( TA = -40oC to + 85oC )

1. Vcc = 1.5V, TA = + 25OC

2. t

RC = Read Cycle Time

3. IccDR_MAX. is 0.7uA at TA=70oC.

DC ELECTRICAL CHARACTERISTICS ( TA = -40oC to + 85oC )

LOW VCC DATA RETENTION WAVEFORM (1) ( CE1 Controlled )

CE1

Data Retention Mode

Vcc

t CDR

Vcc

t R

VIH

Vcc

VDR

1.5V

≥

CE1

Vcc - 0.2V

≥

LOW VCC DATA RETENTION WAVEFORM (2) ( CE2 Controlled )

CE2

Data Retention Mode

Vcc

t CDR

Vcc

t R

VIL

Vcc

VDR ≧ 1.5V

CE2 ≦ 0.2V

PARAMETER

NAME

PARAMETER

TEST CONDITIONS

MIN. TYP. (1) MAX.

UNITS

Vcc=3.0V

VIL

Guaranteed Input Low

Voltage

(3)

Vcc=5.0V

-0.5

--

0.8

V

Vcc=3.0V

2.0

--

VIH

Guaranteed Input High

Voltage

(3)

Vcc=5.0V

2.2

--

Vcc+0.3

V

IIL

Input Leakage Current

Vcc = Max, VIN = 0V to Vcc

--

1

uA

ILO

Output Leakage Current

Vcc = Max, CE1 = VIH or CE2=VIL

or OE = VIH, VI/O = 0V to Vcc

--

1

uA

Vcc=3.0V

VOL

Output Low Voltage

Vcc = Max, IOL = 2.0mA

Vcc=5.0V

--

0.4

V

Vcc=3.0V

VOH

Output High Voltage

Vcc = Min, IOH = -1.0mA

Vcc=5.0V

2.4

--

V

70ns

Vcc=3.0V

--

18

ICC (5)

Operating Power Supply

Current

Vcc=Max,CE1=VIL, CE2=VIH

IDQ = 0mA, F = Fmax

(2)

70ns

Vcc=5.0V

--

45

mA

Vcc=3.0V

--

0.5

ICCSB

Standby Current-TTL

Vcc = Max, CE1 = VIH or CE2=VIL

IDQ = 0mA

Vcc=5.0V

--

1.0

mA

Vcc=3.0V

--

0.3

5

ICCSB1

(4)

Standby Current-CMOS

Vcc = Max, CE1≧Vcc-0.2V or

CE2≦0.2V ;VIN≧ Vcc - 0.2V or

VIN≦0.2V

Vcc=5.0V

--

1.0

30

uA

BS62LV2006

相关PDF资料 |

PDF描述 |

|---|---|

| BS62LV2006TIP70 | Very Low Power/Voltage CMOS SRAM 256K X 8 bit |

| BS62LV2007 | Very Low Power/Voltage CMOS SRAM 256K X 8 bit |

| BS62UV1027JI | 3.3V PLL Clock Driver with LVPECL Input and 12 LVTTL Outputs 52-TQFP |

| BS62UV1027PC | Ultra Low Power/Voltage CMOS SRAM 128K X 8 bit |

| BS62UV1027PI | 3.3V PLL CLock Driver with 1/2x, 1x and 2x Frequency Options 52-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BS62LV2006TIP70 | 制造商:BSI 制造商全称:Brilliance Semiconductor 功能描述:Very Low Power CMOS SRAM 256K X 8 bit |

| BS62LV2007 | 制造商:BSI 制造商全称:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K X 8 bit |

| BS62LV2007HC | 制造商:BSI 制造商全称:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K X 8 bit |

| BS62LV2007HI | 制造商:BSI 制造商全称:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K X 8 bit |

| BS62LV2008 | 制造商:BSI 制造商全称:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K X 8 bit |

发布紧急采购,3分钟左右您将得到回复。