- 您现在的位置:买卖IC网 > PDF目录210377 > BU-61865F3-160K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF资料下载

参数资料

| 型号: | BU-61865F3-160K |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封装: | 25.40 X 25.40 MM, 3.94 MM HEIGHT, CERAMIC, FP-72 |

| 文件页数: | 9/60页 |

| 文件大小: | 457K |

| 代理商: | BU-61865F3-160K |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

17

Data Device Corporation

www.ddc-web.com

BU-6174X/6184X/6186X

F-10/02-300

tain an address value that is modulo 8. Also, note that if the

message is an RT-to-RT transfer, the pointer parameter must

contain an address value that is modulo 16.

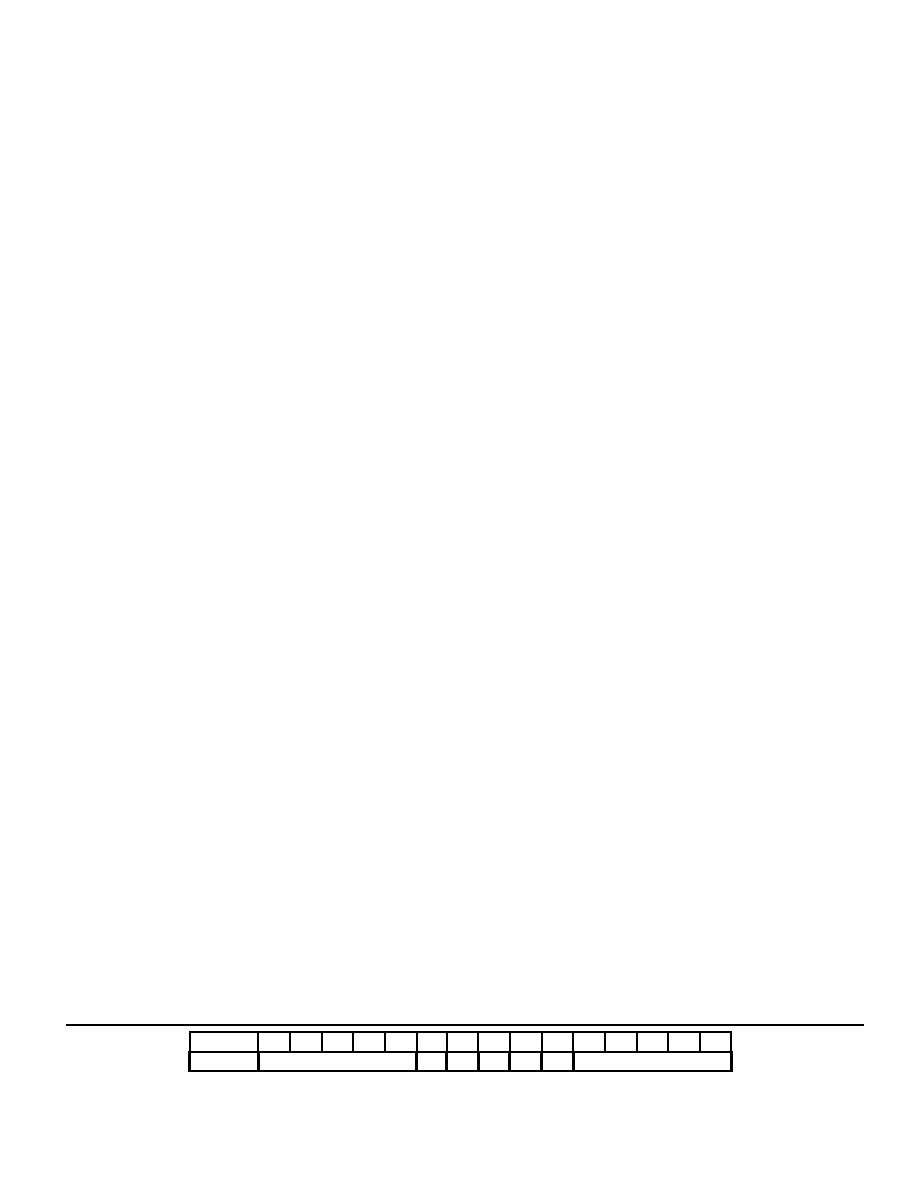

OP CODES

The instruction list pointer register references a pair of words in

the BC instruction list: an op code word, followed by a parameter

word. The format of the op code word, which is illustrated in FIG-

URE 3, includes a 5-bit op code field and a 5-bit condition code

field. The op code identifies the instruction to be executed by the

BC message sequence controller.

Most of the operations are conditional, with execution dependent

on the contents of the condition code field. Bits 3-0 of the condi-

tion code field identifies a particular condition. Bit 4 of the condi-

tion code field identifies the logic sense ("1" or "0") of the select-

ed condition code on which the conditional execution is depen-

dent. TABLE 36 lists all the op codes, along with their respective

mnemonic, code value, parameter, and description. TABLE 37

defines all the condition codes.

Eight of the condition codes (8 through F) are set or cleared as

the result of the most recent message. The other eight are

defined as "General Purpose" condition codes GP0 through

GP7. There are three mechanisms for programming the values of

the General Purpose Condition Code bits: (1) They may be set,

cleared, or toggled by the host processor, by means of the BC

GENERAL PURPOSE FLAG REGISTER; (2) they may be set,

cleared, or toggled by the BC message sequence control

processor, by means of the GP Flag Bits (FLG) instruction; and

(3) GP0 and GP1 only (but none of the others) may be set or

cleared by means of the BC message sequence control proces-

sor's Compare Frame Timer (CFT) or Compare Message Timer

(CMT) instructions.

The host processor also has read-only access to the BC condi-

tion codes by means of the BC CONDITION CODE REGISTER.

Note that four (4) instructions are unconditional. These are

Compare to Frame Timer (CFT), Compare to Message Timer

(CMT), GP Flag Bits (FLG), and Execute and Flip (XQF). For

these instructions, the Condition Code Field is "don't care". That

is, these instructions are always executed, regardless of the

result of the condition code test.

All of the other instructions are conditional. That is, they will only be

executed if the condition code specified by the condition code field

in the op code word tests true. If the condition code field tests false,

the instruction list pointer will skip down to the next instruction.

As shown in TABLE 36, many of the operations include a single-

word parameter. For an XEQ (execute message) operation, the

parameter is a pointer to the start of the message’s Control /

Status block. For other operations, the parameter may be an

address, a time value, an interrupt pattern, a mechanism to set

or clear general purpose flag bits, or an immediate value. For

several op codes, the parameter is "don't care" (not used).

As described above, some of the op codes will cause the mes-

sage sequence control processor to execute messages. In this

case, the parameter references the first word of a message

Control/Status block. With the exception of RT-to-RT transfer

messages, all message status/control blocks are eight words

long: a block control word, time-to-next-message parameter,

data block pointer, command word, status word, loopback word,

block status word, and time tag word.

In the case of an RT-to-RT transfer message, the size of the mes-

sage control/status block increases to 16 words. However, in this

case, the last six words are not used; the ninth and tenth words are

for the second command word and second status word.

The third word in the message control/status block is a pointer

that references the first word of the message's data word block.

Note that the data word block stores only data words, which are

to be either transmitted or received by the BC. By segregating

data words from command words, status words, and other con-

trol and "housekeeping" functions, this architecture enables the

use of convenient, usable data structures, such as circular

buffers and double buffers.

Other operations support program flow control; i.e., jump and call

capability. The call capability includes maintenance of a call

stack which supports a maximum of four (4) entries; there is also

a return instruction. In the case of a call stack overrun or under-

run, the BC will issue a CALL STACK POINTER REGISTER

ERROR interrupt, if enabled.

Other op codes may be used to delay for a specified time; start

a new BC frame; wait for an external trigger to start a new frame;

perform comparisons based on frame time and time-to-next

message; load the time tag or frame time registers; halt; and

issue host interrupts. In the case of host interrupts, the message

control processor passes a 4-bit user-defined interrupt vector to

the host, by means of the Enhanced Mini-ACE/-ACE's Interrupt

Status Register.

The purpose of the FLG instruction is to enable the message

sequence controller to set, clear, or toggle the value(s) of any or

all of the eight general purpose condition flags.

The op code parity bit encompasses all sixteen bits of the op

code word. This bit must be programmed for odd parity. If the

message sequence control processor fetches an undefined op

code word, an op code word with even parity, or bits 9-5 of an op

code word do not have a binary pattern of 01010, the message

sequence control processor will immediately halt the BC's oper-

ation. In addition, if enabled, a BC TRAP OP CODE interrupt will

be issued. Also, if enabled, a parity error will result in an OP

CODE PARITY ERROR interrupt. TABLE 37 describes the

Condition Codes.

FIGURE 3. BC OP CODE FORMAT

15

10

11

12

13

14

5

6

7

8

9

0

1

2

3

4

Odd Parity

0

OpCode Field

1

0

Condition Code Field

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61865F3-172L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865F4-120Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865G3-110Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865G3-150K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865G3-172Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61865F4-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| BU-61865F4-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| BU-61865G3-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| BU-61865G3-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| BU-61865G4-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

发布紧急采购,3分钟左右您将得到回复。