- 您现在的位置:买卖IC网 > PDF目录255929 > BUS-65164-100 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 PDF资料下载

参数资料

| 型号: | BUS-65164-100 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| 封装: | 1.900 X 1 INCH, 0.215 INCH HEIGHT, FP-70 |

| 文件页数: | 1/40页 |

| 文件大小: | 349K |

| 代理商: | BUS-65164-100 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

DESCRIPTION

The BUS-65153 is a complete, dual

redundant MIL-STD-1553B Remote

Terminal. Packaged in a 1.9" x 1.0" x

0.2", 70-pin ceramic package, the

BUS-65153 provides the transmitter

voltage level required by MIL-STD-

1760. Also in support of MIL-STD-

1760, the RT address inputs are

latchable.

The BUS-65153 contains two low power

transceivers and a DDC custom designed

chip.

This

chip

includes

dual

encoder/decoder, RT protocol logic, tri-

state data buffers, and DMA transfer con-

trol logic. The BUS-65153 supports all 13

dual redundant mode codes, any combi-

nation of which may be illegalized by an

external PROM, PLD, or RAM device.

Parallel data transfers are accomplished

via a DMA type interface. Both 8-bit and

16-bit transfers are supported.

The BUS-65153 can be easily inter-

faced to most CPU's. In addition, the

BUS-65153 can interface directly to

minimum

complexity

subsystems

such as switches, D/A converters,

etc.

The address bus and transfer control sig-

nals may be configured for either two-state

or three-state operation. Use of the three-

state address mode reduces the number

of external components required for a

DMA processor interface.

The input clock frequency is user

selectable for either 12 or 16 MHz. In the

12 MHz mode, the decoder operates at 24

MHz, providing superior word error rate

and zero crossing distortion tolerance. The

Busy, Service Request, and Subsystem

Flag RT Status Word bits are provided as

discrete pins, allowing for easy access by

the subsystem.

Various message timing and error

flag indicators are provided to facili-

tate the subsystem interface.

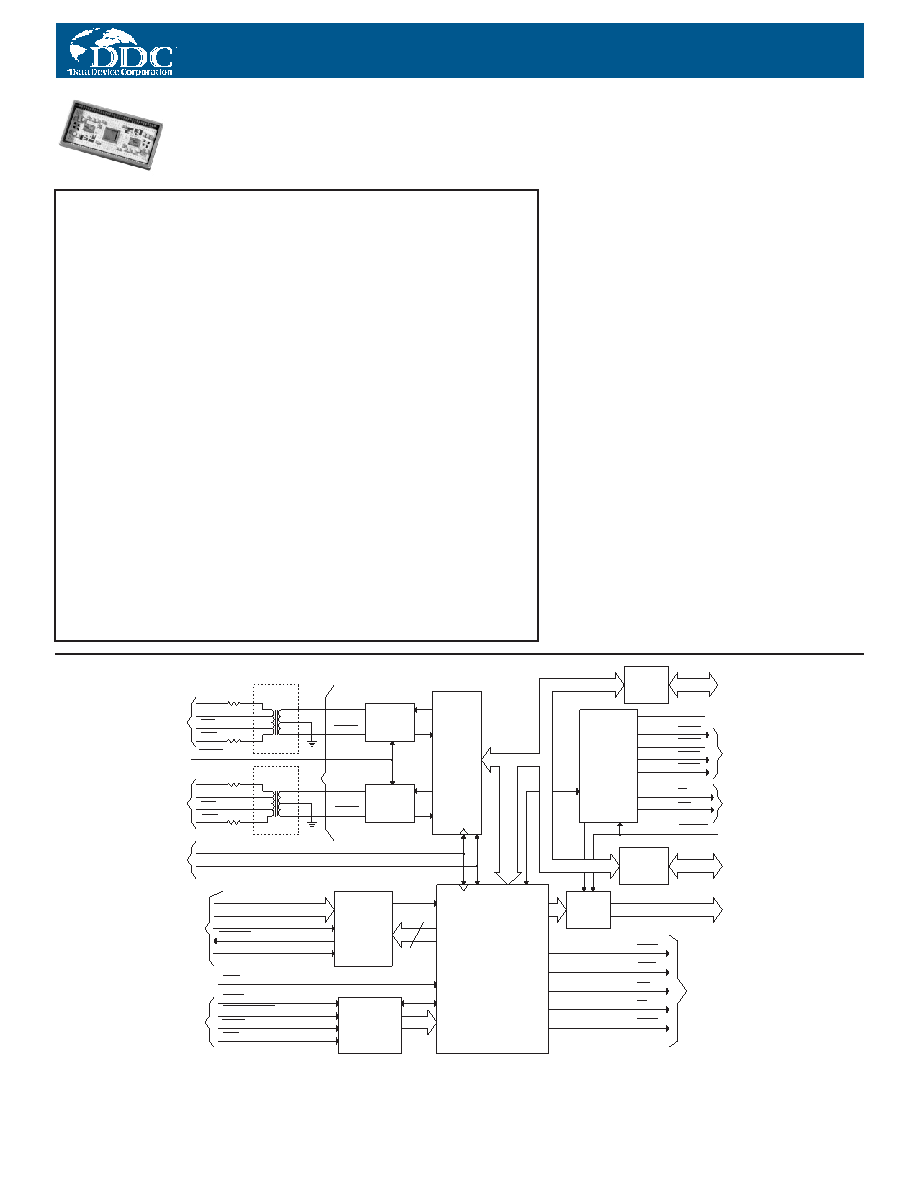

MIL-STD-1553B, NOTICE 2 AND MIL-STD-1760B

SMALL TERMINAL INTERFACE CIRCUIT “STIC”

*

UPPER

DATA BUS

UPPER DATA

BUFFER

D15-D8

DB_SEL

BUS-25679

8

7

1

TX/RX A

55 ohms

A DIR

A XF

55 ohms

BUS A

BUS B

TX_INH

TRANSMITTER

INHIBIT

A XF

A DIR

B DIR

B XF

B DIR

BUS-25679

5

4

8

7

5

4

1

3

TX/RX A

TX/RX B

1553

BUS

I/O

2

TRANSCEIVER

A

TRANSCEIVER

B

ENCODER/

DECODER AND

WATCHDOG

TIMER

DMA HANDSHAKE

CONTROL LOGIC

AND TRANSFER

DT_REQ

DT_GRT

DT_ACK

HS_FAIL

CS

WRT

WIDTH SELECT

DMA

HANDSHAKE

DATA

TRANSFER

CONTROL

ADDRESS

14-BIT

ADDRESS

BUS

LOWER

DATA BUS

TRI-STATE

CONTROL

A13-A0

LOWER DATA

BUFFER

D7-D0

ADDR_ENA

ADDRESS

BUFFERS

REGISTERS

5

R.T. ADDRESS

PARITY AND

COMPARE LOGIC

55 ohms

CLK

CLK_SEL

RT_AD4-RT_AD0

RT_AD_P

RT_AD_ERR

R.T.

CLOCK INPUT

AND

FREQUENCY

SELECT

RT_AD_LAT

ADDRESS

RESET

SSFLAG

BUSY

ILLEGALIZATION

AND STATUS

INPUTS

ILLCMD

SERVICE_REQUEST

RESET

AND

TRANSMITTER

INHIBIT LOGIC

STATUS,

ILLEGALIZATION,

LAST COMMAND, STATUS,

CURRENT COMMAND,

AND BIT WORD

R.T. STATE

AND

MACHINE

LOGIC

NBGRT

INCMD

GBR

ME

RT_FAIL

MESSAGE

TIMING

SIGNALS

*

1991, 1999 Data Device Corporation

FIGURE 1. BUS-65153 BLOCK DIAGRAM

FEATURES

Supports MIL-STD-1553B Notice 2

and MIL-STD-1760 Stores

Management

Complete Integrated Remote

Terminal Including:

- Dual Low-Power Transceiver

- Complete RT Protocol Logic

Small, 70-Pin Ceramic Package

Meets 1553A/McAir Response Time

Requirements

Selectable 8/16-bit DMA Interface

Optional Tri-State Address Bus and

Transfer Control Signals

Direct Interface to Simple Systems

Selectable Input Clock, 12 or 16

MHz

MIL-PRF-38534 Processing

Available

Note: Transformers are external

BUS-65153

相关PDF资料 |

PDF描述 |

|---|---|

| BUS-65164-110 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BUS-65164-300 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BUS-65153-110 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BQ4845S-N | 0 TIMER(S), REAL TIME CLOCK, PDSO28 |

| BQ4845YP-N | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-S802 | 制造商:Fuji Electric 功能描述: |

| BU-S803 | 制造商:Fuji Electric 功能描述: |

| BUS98 | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

| BUS98/D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SWITCHMODE? Series NPN Silicon Power Transistors |

| BUS98A | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

发布紧急采购,3分钟左右您将得到回复。