参数资料

| 型号: | CA3338MZ96 |

| 厂商: | Intersil |

| 文件页数: | 7/10页 |

| 文件大小: | 0K |

| 描述: | IC CONV D/A 8BIT 50MHZ 16-SOIC |

| 标准包装: | 1,000 |

| 设置时间: | 20ns |

| 位数: | 8 |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 1 电压,单极;1 电压,双极 |

| 采样率(每秒): | 50M |

6

CA3338, CA3338A

In bipolar operation, VREF- would be returned to a negative

voltage (the maximum voltage rating to VDD must be

observed). VEE, which supplies the gate potential for the

output drivers, must be returned to a point at least as

negative as VREF-. Note that the maximum clocking speed

decreases when the bipolar mode is used.

Static Characteristics

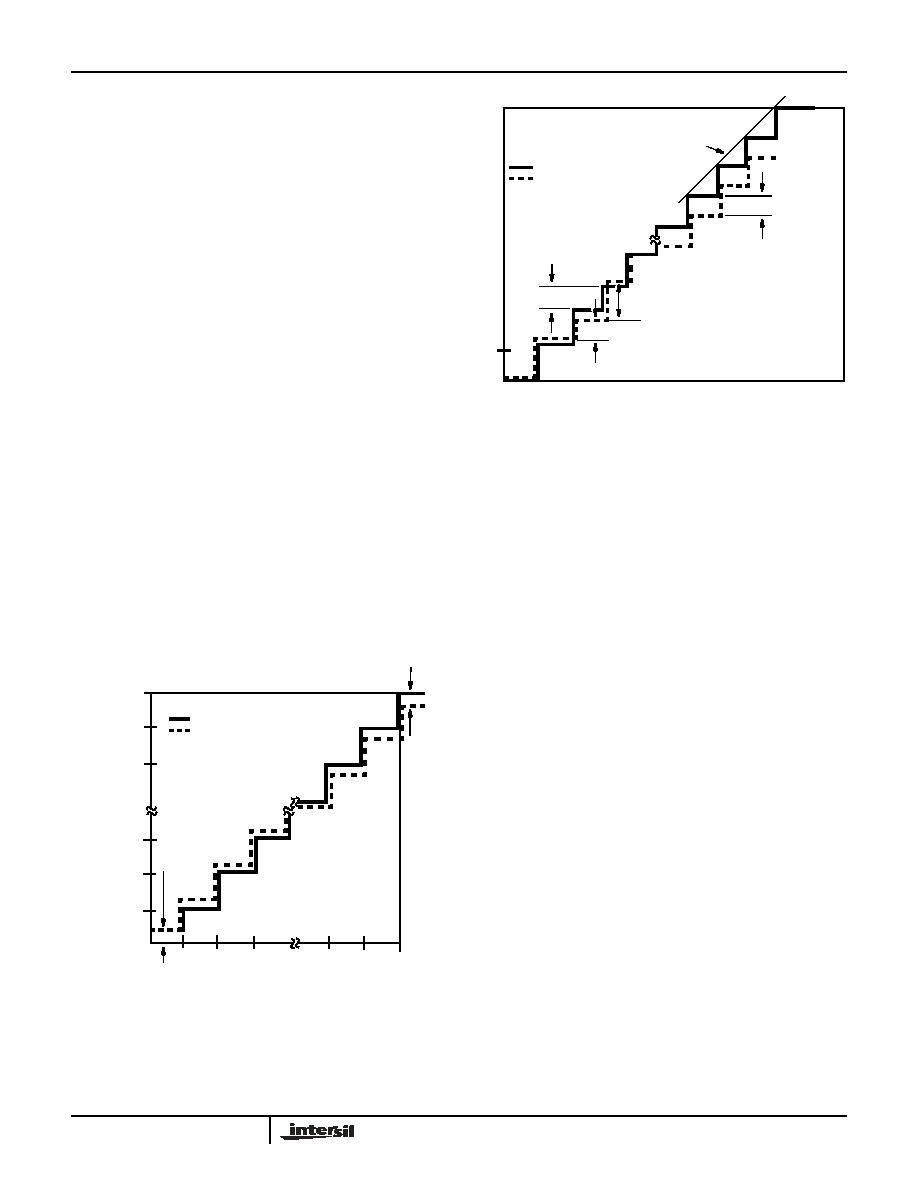

The ideal 8-bit D/A would have an output equal to VREF- with

an input code of 00HEX (zero scale output), and an output

equal to 255/256 of VREF+ (referred to VREF-) with an input

code of FFHEX (full scale output). The difference between the

ideal and actual values of these two parameters are the

OFFSET and GAIN errors, respectively; see Figure 3.

If the code into an 8-bit D/A is changed by 1 count, the output

should change by 1/255 (full scale output - zero scale output). A

deviation from this step size is a differential linearity error, see

Figure 4. Note that the error is expressed in fractions of the

ideal step size (usually called an LSB). Also note that if the (-)

differential linearity error is less (in absolute numbers) than 1

LSB, the device is monotonic. (The output will always increase

for increasing code or decrease for decreasing code).

If the code into an 8-bit D/A is at any value, say “N”, the output

voltage should be N/255 of the full scale output (referred to the

zero scale output). Any deviation from that output is an integral

linearity error, usually expressed in LSBs. See Figure 4.

Note that OFFSET and GAIN errors do not affect integral

linearity, as the linearity is referenced to actual zero and full

scale outputs, not ideal. Absolute accuracy would have to

also take these errors into account.

Dynamic Characteristics

Keeping the full-scale range (VREF+ - VREF-) as high as

possible gives the best linearity and lowest “glitch” energy

(referred to 1V). This provides the best “P” and “N” channel

gate drives (hence saturation resistance) and propagation

delays. The VREF+ (and VREF- if bipolar) terminal should be

well bypassed as near the chip as possible.

“Glitch” energy is defined as a spurious voltage that occurs as

the output is changed from one voltage to another. In a binary

input converter, it is usually highest at the most significant bit

transition (7FHEX to 80HEX for an 8 bit device), and can be

measured by displaying the output as the input code

alternates around that point. The “glitch” energy is the area

between the actual output display and an ideal one LSB step

voltage (subtracting negative area from positive), at either the

positive or negative-going step. It is usually expressed in pV/s.

The CA3338 uses a modified R2R ladder, where the 3 most

significant bits drive a bar graph decoder and 7 equally

weighted resistors. This makes the “glitch” energy at each 1/8

scale transition (1FHEX to 20HEX, 3FHEX to 40HEX, etc.)

essentially equal, and far less than the MSB transition would

otherwise display.

For the purpose of comparison to other converters, the output

should be resistively divided to 1V full scale. Figure 5 shows a

typical hook-up for checking “glitch” energy or settling time.

The settling time of the A/D is mainly a function of the output

resistance (approximately 160

in parallel with the load

resistance) and the load plus internal chip capacitance. Both

“glitch” energy and settling time measurements require very

good circuit and probe grounding: a probe tip connector such

as Tektronix part number 131-0258-00 is recommended.

255/256

254/256

253/256

3/256

2/256

1/256

0

00

01

02

03

FD

FE

FF

= IDEAL TRANSFER CURVE

= ACTUAL TRANSFER CURVE

OFFSET

ERROR

(SHOWN +)

OUTPUT

V

O

L

T

A

G

E

AS

A

FRA

C

TION

OF

V

REF

+

-

V

RE

F

-

GAIN ERROR

(SHOWN -)

INPUT CODE IN HEXADECIMAL (COMP = LOW)

FIGURE 3. D/A OFFSET AND GAIN ERROR

0

00

OUT

P

UT

V

O

L

T

A

G

E

C

B

FROM “0” SCALE

INTEGRAL LINEARITY

ERROR (SHOWN -)

STRAIGHT LINE

TO FULL SCALE

VOLTAGE

INPUT CODE

= IDEAL TRANSFER CURVE

= ACTUAL TRANSFER CURVE

A = IDEAL STEP SIZE (1/255 OF FULL

B - A = +DIFFERENTIAL LINEARITY ERROR

C - A = -DIFFERENTIAL LINEARITY ERROR

A

SCALE -“0” SCALE VOLTAGE)

FIGURE 4. D/A INTEGRAL AND DIFFERENTIAL LINEARITY

ERROR

相关PDF资料 |

PDF描述 |

|---|---|

| LT6552IDD#TR | IC OPAMP VID DIFF SGL 3.3V 8-DFN |

| ISL5629INZ | IC DAC DUAL 8BIT 3.3V 48-LQFP |

| LT1252CS8#TRPBF | IC AMP VIDEO LOW COST SNGL 8SOIC |

| VE-B3V-MU-F1 | CONVERTER MOD DC/DC 5.8V 200W |

| VI-J4F-MW-S | CONVERTER MOD DC/DC 72V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CA3350-000 | 制造商:TE Connectivity 功能描述:Hook-up Wire 制造商:TE Connectivity 功能描述:FLHTC0311-26-6CS3125 - Bulk |

| CA3355-000 | 制造商:TE Connectivity 功能描述:HMM-699318-2.5-8A |

| CA3362-000 | 制造商:TE Connectivity 功能描述:VPB-1-0-SP-CS7733 |

| CA3364-000 | 制造商:TE Connectivity 功能描述:MTCTQ-YH1-P22 - Bulk |

| CA337-158M050BE | 功能描述:铝质电解电容器 - 带引线 1500UF 50V RoHS:否 制造商:Kemet 引线类型: 电容:220 uF 容差:20 % 电压额定值:25 V 工作温度范围: 端接类型:Radial 外壳直径:8 mm 外壳长度:11 mm 引线间隔:5 mm 产品:General Purpose Electrolytic Capacitors 封装:Bulk |

发布紧急采购,3分钟左右您将得到回复。