- 您现在的位置:买卖IC网 > PDF目录298899 > CAT1024ZD4I-45-T2 (ON SEMICONDUCTOR) 1-CHANNEL POWER SUPPLY SUPPORT CKT, DSO8 PDF资料下载

参数资料

| 型号: | CAT1024ZD4I-45-T2 |

| 厂商: | ON SEMICONDUCTOR |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY SUPPORT CKT, DSO8 |

| 封装: | 3 X 3 MM, 0.80 MM HEIGHT, ROHS COMPLIANT, TDFN-8 |

| 文件页数: | 5/20页 |

| 文件大小: | 228K |

| 代理商: | CAT1024ZD4I-45-T2 |

CAT1024, CAT1025

Catalyst Semiconductor, Inc.

13

Doc. No. MD-3008 Rev. O

Characteristics subject to change without notice

Immediate/Current Address Read

The CAT1024 and CAT1025 address counter

contains the address of the last byte accessed,

incremented by one. In other words, if the last READ

or WRITE access was to address N, the READ

immediately following would access data from

address N + 1. For N = E = 255, the counter will

wrap around to zero and continue to clock out valid

data. After the CAT1024/1025 receives its slave

address information (with the R/W

bit set to one), it

issues an acknowledge, then transmits the 8-bit byte

requested. The master device does not send an

acknowledge, but will generate a STOP condition.

Selective/Random Read

Selective/Random READ operations allow the

Master device to select at random any memory

location for a READ operation. The Master device

first performs a ‘dummy’ write operation by sending

the START condition, slave address and byte

addresses of the location it wishes to read. After the

CAT1024 and CAT1025 acknowledges, the Master

device sends the START condition and the slave

address again, this time with the R/W

bit set to one.

The CAT1024 and CAT1025 then responds with its

acknowledge and sends the 8-bit byte requested.

The master device does not send an acknowledge

but will generate a STOP condition.

Sequential Read

The Sequential READ operation can be initiated by

either the Immediate Address READ or Selective READ

operations. After the CAT1024 and CAT1025 sends the

inital 8-bit byte requested, the Master will responds with

an acknowledge which tells the device it requires more

data. The CAT1024 and CAT1025 will continue to

output an 8-bit byte for each acknowledge, thus sending

the STOP condition.

The data being transmitted from the CAT1024 and

CAT1025 is sent sequentially with the data from

address N followed by data from address N + 1. The

READ operation address counter increments all of the

CAT1024 and CAT1025 address bits so that the entire

memory array can be read during one operation.

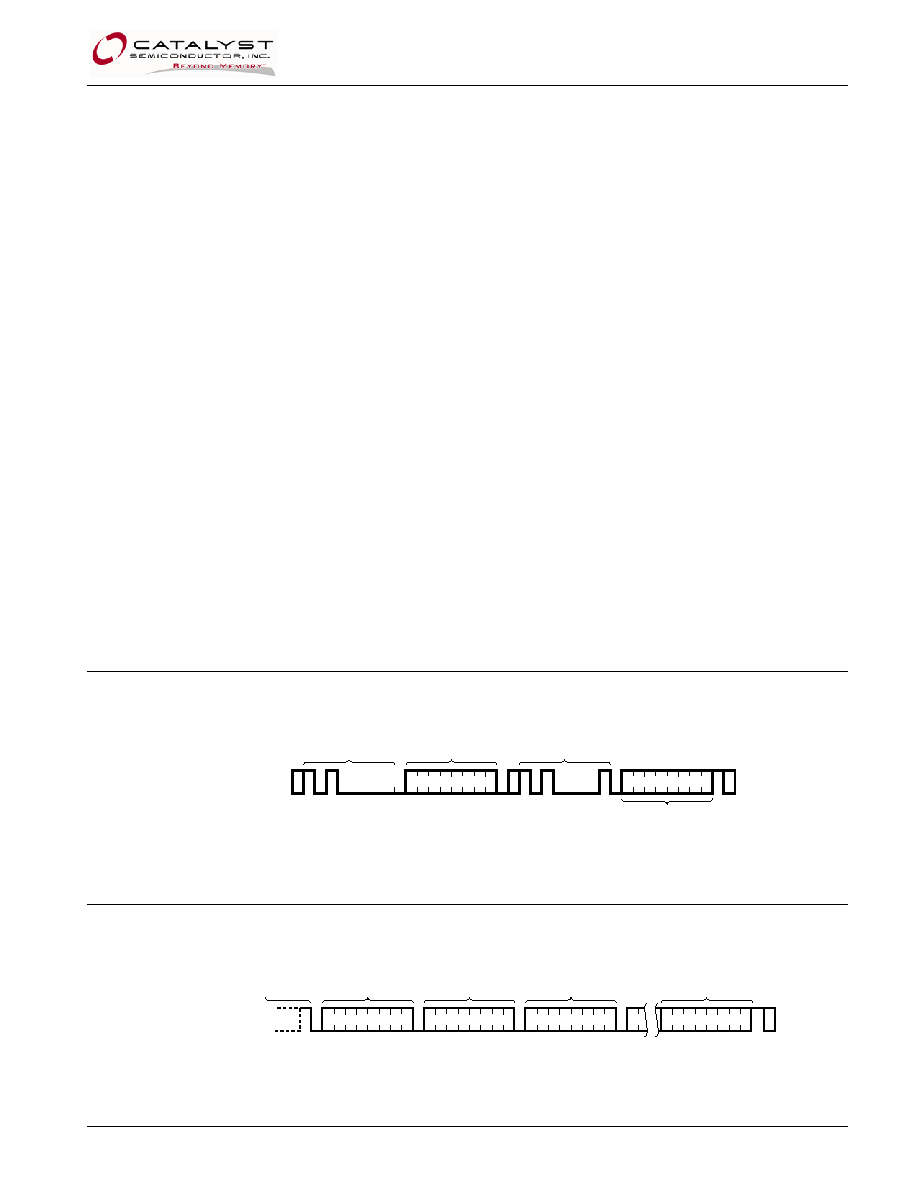

Figure 11. Selective Read Timing

Figure 12. Sequential Read Timing

SLAVE

ADDRESS

S

A

C

K

N

O

A

C

K

S

T

O

P

BUS ACTIVITY:

MASTER

SDA LINE

S

T

A

R

T

BYTE

ADDRESS (n)

S

A

C

K

DATA n

SLAVE

ADDRESS

A

C

K

S

T

A

R

T

BUS ACTIVITY:

MASTER

SDA LINE

DATA n+x

DATA n

A

C

K

A

C

K

DATA n+1

A

C

K

S

T

O

P

N

O

A

C

K

DATA n+2

A

C

K

P

SLAVE

ADDRESS

相关PDF资料 |

PDF描述 |

|---|---|

| CAT1161PI-30 | I2C Serial EEPROM with Supervisory Features |

| CAT1161PI-42 | I2C Serial EEPROM with Supervisory Features |

| CAT1161PI-45 | I2C Serial EEPROM with Supervisory Features |

| CAT1162J-25 | I2C Serial EEPROM with Supervisory Features |

| CAT1162J-28 | 1.25A SCRS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT1024ZD4I-45T3 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024ZD4I-45TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024ZE-25TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024ZE-28TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024ZE-30TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

发布紧急采购,3分钟左右您将得到回复。