- 您现在的位置:买卖IC网 > PDF目录298899 > CAT22C10PA-30 NVRAM (EEPROM Based) PDF资料下载

参数资料

| 型号: | CAT22C10PA-30 |

| 英文描述: | NVRAM (EEPROM Based) |

| 中文描述: | NVRAM中(EEPROM的基础) |

| 文件页数: | 9/10页 |

| 文件大小: | 107K |

| 代理商: | CAT22C10PA-30 |

CAT22C10

8

Doc. No. 25018-0A 2/98 N-1

Recall

At anytime, except during a store operation, taking the

RECALL pin low will initiate a recall operation. This is

independent of the state of

CS, WE, or A0–A5. After the

RECALL pin has been held low for the duration of the

Recall Pulse Width (tRCP), the recall will continue inde-

pendent of any other inputs. During the recall, the entire

contents of the E2PROM array is transferred to the Static

RAM array. The first byte of data may be externally

accessed after the recalled data access time from end of

recall (tARC) is met. After this, any other byte may be

accessed by using the normal read mode.

If the

RECALL pin is held low for the entire Recall Cycle

time (tRCC), the contents of the Static RAM may be

immediately accessed by using the normal read mode.

A recall operation can be performed an unlimited num-

ber of times without affecting the integrity of the data.

The outputs I/O0–I/O3 will go into the high impedance

state as long as the

RECALL signal is held low.

Store

At any time, except during a recall operation, taking the

STORE pin low will initiate a store operation. This takes

place independent of the state of

CS, WE or A0–A5. The

STORE pin must be held low for the duration of the Store

Pulse Width (tSTP) to ensure that a store operation is

initiated. Once initiated, the

STORE pin becomes a

“Don’t Care”, and the store operation will complete its

transfer of the entire contents of the Static RAM array

into the E2PROM array within the Store Cycle time

(tSTC). If a store operation is initiated during a write cycle,

the contents of the addressed Static RAM byte and its

corresponding byte in the E2PROM array will be un-

known.

During the store operation, the outputs are in a high

impedance state. A minimum of 100,000 store opera-

tions can be performed reliably and the data written into

the E2PROM array has a minimum data retention time

of 10 years.

DATA PROTECTION DURING POWER-UP AND

POWER-DOWN

The CAT22C10 has on-chip circuitry which will prevent

a store operation from occurring when VCC falls below

3.0V typ. This function eliminates the potential hazard of

spurious signals initiating a store operation when the

system power is below 3.0V typ.

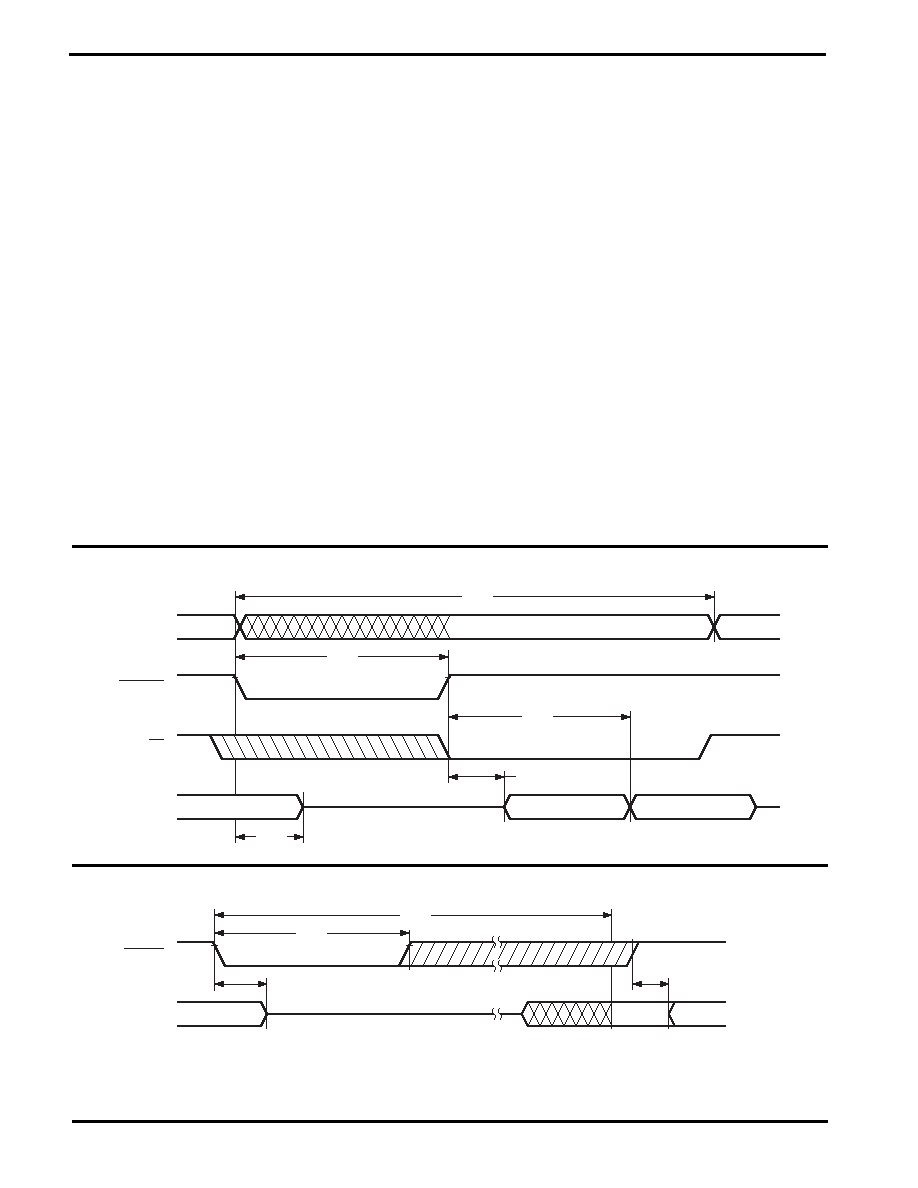

Figure 4. Recall Cycle Timing

5153 FHD F08

5153 FHD F07

Figure 5. Store Cycle Timing

CS

DATA I/O

RECALL

ADDRESS

DATA UNDEFINED

DATA VALID

HIGH-Z

tRCZ

tORC

tARC

tRCP

tRCC

STORE

DATA I/O

tSTZ

tOST

HIGH-Z

tSTP

tSTC

This Material Copyrighted by Its Respective Manufacturer

相关PDF资料 |

PDF描述 |

|---|---|

| CAT22C10PI-20 | NVRAM (EEPROM Based) |

| CAT22C10PI-30 | NVRAM (EEPROM Based) |

| CAT22C12P-20 | NVRAM (EEPROM Based) |

| CAT22C12P-30 | NVRAM (EEPROM Based) |

| CAT22C12PA-20 | NVRAM (EEPROM Based) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT22C10PA-30TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10PA-30-TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10PI-20 | 功能描述:NVRAM 256bit (64x4) 5V RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube |

| CAT22C10PI-20TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10PI-20-TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

发布紧急采购,3分钟左右您将得到回复。