- 您现在的位置:买卖IC网 > PDF目录298902 > CAT24C04J-TE13 I2C Serial EEPROM PDF资料下载

参数资料

| 型号: | CAT24C04J-TE13 |

| 英文描述: | I2C Serial EEPROM |

| 中文描述: | I2C串行EEPROM的 |

| 文件页数: | 6/7页 |

| 文件大小: | 92K |

| 代理商: | CAT24C04J-TE13 |

CAT24C01B

6

Doc. No. 25085-00 7/99 S-1

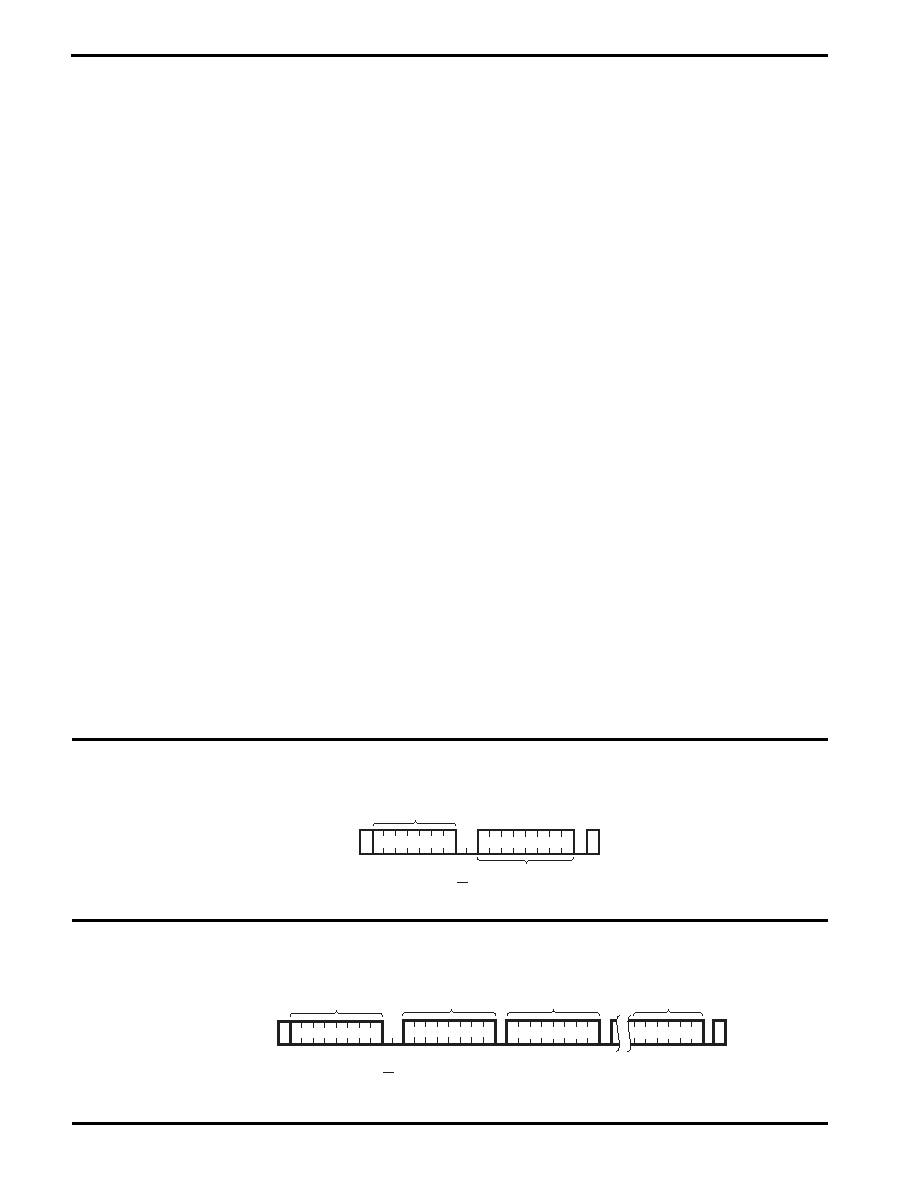

Figure 6. Page Write Timing

Figure5. Byte Write Timing

ing with an acknowledge and by issuing a stop condition.

Refer to Figure 7 for the start word address, read bit,

acknowledge and data transfer sequence.

Sequential Read

The Sequential READ operation can be initiated after

the 24C01B sends the initial 8-bit byte requested, the

Master will respond with an acknowledge which tells the

device it requires more data. The CAT24C01B will

continue to output an 8-bit byte for each acknowledge

sent by the Master. The operation is terminated when

the Master fails to respond with an acknowledge, thus

sending the STOP condition.

The data being transmitted from the CAT24C01B is

output sequentially with data from address N followed by

data from address N+1. The READ operation address

counter increments all of the CAT24C01B address bits

so that the entire memory array can be read during one

operation. If more than bytes are read out, the counter

will “wrap around” and continue to clock out data bytes.

Acknowledge Polling

The disabling of the inputs can be used to take advan-

tage of the typical write cycle time. Once the stop

condition is issued to indicate the end of the host’s write

operation, the CAT24C01B initiates the internal write

cycle. ACK polling can be initiated immediately. This

involves issuing the start condition followed by the byte

address for a write operation. If the CAT24C01B is still

busy with the write operation, no ACK will be returned.

If the CAT24C01B has completed the write operation, an

ACK will be returned and the host can then proceed with

the next read or write operation.

READ OPERATIONS

The READ operation for the CAT24C01B is initiated in

the same manner as the write operation with the one

exception that the R/

W bit is set to a one. Two different

READ operations are possible: Byte READ and Se-

quential READ.

It should be noted that the ninth clock cycle of the read

operation is not a "don't care." To terminate a read

operation, the master must either issure a stop condition

during the ninth cycle or hold SDA HIGH during the ninth

clock cycle and then issue a stop condition.

Byte Read

To initiate a read operation, the master sends a start

condition followed by a seven bit word address and a

read bit. The CAT24C01B responds with an acknowl-

edge and then transmits the eight bits of data. The read

operation is terminated by the master; by not respond-

BUS ACTIVITY:

SDA LINE

DATA n+3

A

C

K

A

C

K

DATA n

S

T

O

P

S

A

C

K

DATA n+1

A

C

K

S

T

A

R

T

P

WORD

ADDRESS(n)

M

S

B

L

S

B

R

/

W

BUS ACTIVITY:

SDA LINE

A

C

K

A

C

K

DATA n

S

T

O

P

S

T

A

R

T

P

WORD

ADDRESS(n)

M

S

B

L

S

B

R

/

W

BUS ACTIVITY:

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相关PDF资料 |

PDF描述 |

|---|---|

| CAT24C04J-TE7 | I2C Serial EEPROM |

| CAT24C04P | I2C Serial EEPROM |

| CAT24C04P-1.8 | I2C Serial EEPROM |

| CAT24C04P-2.5 | I2C Serial EEPROM |

| CAT24C04P-2.7 | I2C Serial EEPROM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT24C04J-TE7 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

| CAT24C04LE.G | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:1-Kb, 2-Kb, 4-Kb, 8-Kb and 16-Kb I2C CMOS Serial EEPROM |

| CAT24C04LE-G | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:1-Kb, 2-Kb, 4-Kb, 8-Kb and 16-Kb I2C CMOS Serial EEPROM PDIPa??8 L SUFFIX |

| CAT24C04LE-GT3 | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:1-Kb, 2-Kb, 4-Kb, 8-Kb and 16-Kb I2C CMOS Serial EEPROM |

| CAT24C04LE-T3 | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:1-Kb, 2-Kb, 4-Kb, 8-Kb and 16-Kb I2C CMOS Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。