- 您现在的位置:买卖IC网 > PDF目录20022 > CAT28F001G-12T (ON Semiconductor)IC FLASH 1MBIT 120NS 32PLCC PDF资料下载

参数资料

| 型号: | CAT28F001G-12T |

| 厂商: | ON Semiconductor |

| 文件页数: | 10/18页 |

| 文件大小: | 0K |

| 描述: | IC FLASH 1MBIT 120NS 32PLCC |

| 产品变化通告: | Product Obsolescence 05/Oct/2010 |

| 标准包装: | 32 |

| 格式 - 存储器: | 闪存 |

| 存储器类型: | FLASH |

| 存储容量: | 1M (128K x 8) |

| 速度: | 120ns |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 32-LCC(J 形引线) |

| 供应商设备封装: | 32-PLCC(11.43x13.97) |

| 包装: | 管件 |

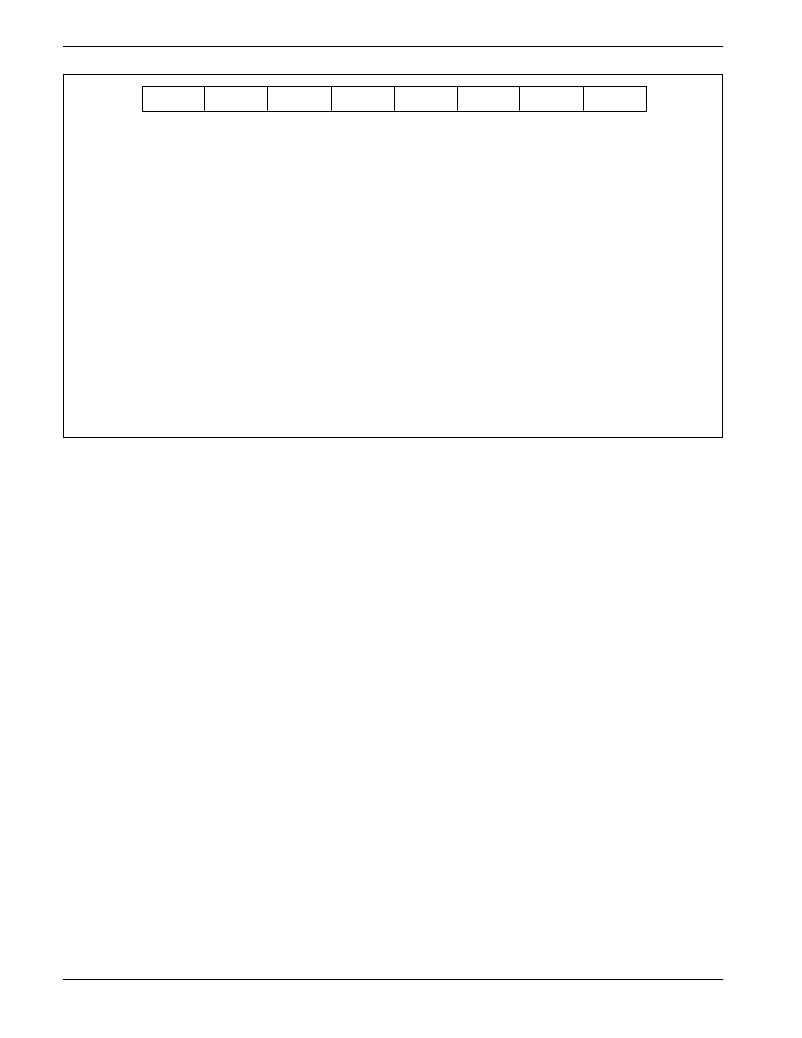

�� �

�

CAT28F001�

�WSMS�

�7�

�ESS�

�6�

�ES�

�5�

�PS�

�4�

�VPPS�

�3�

�R�

�2�

�R�

�1�

�R�

�0�

�SR.7� =� WRITE� STATE� MACHINE� STATUS�

�1� =� Ready�

�0� =� Busy�

�SR.6� =� ERASE� SUSPEND� STATUS�

�1� =� Erase� Suspended�

�0� =� Erase� in� Progress/Completed�

�SR.5� =� ERASE� STATUS�

�1� =� Error� in� Block� Erasure�

�0� =� Successful� Block� Erase�

�SR.4� =� PROGRAM� STATUS�

�1� =� Error� in� Byte� Program�

�0� =� Successful� Byte� Program�

�SR.3� =� VPP� STATUS�

�1� =� V� PP� Low� Detect;� Operation� Abort�

�0� =� V� PP� Okay�

�SR.2� -SR.0� =� RESERVED� FOR� FUTURE� ENHANCEMENTS�

�These� bits� are� reserved� for� future� use� and� should� be� masked�

�out� when� polling� the� Status� Register.�

�When� the� Status� Register� indicates� that� programming� is�

�complete,� the� Program� Status� bit� should� be� checked.� If�

�program� error� is� detected,� the� Status� Register� should� be�

�cleared.� The� internal� WSM� verify� only� detects� errors� for�

�“1s”� that� do� not� successfully� program� to� “0s”.� The�

�Command� Register� remains� in� Read� Status� Register�

�mode� until� further� commands� are� issued� to� it.�

�If� erase/byte� program� is� attempted� while� V� PP� =� V� PPL� ,� the�

�Status� bit� (SR.5/SR.4)� will� be� set� to� “1”.� Erase/Program�

�attempts� while� V� PPL� <� V� PP� <� V� PPH� produce� spurious�

�results� and� should� not� be� attempted.�

�EMBEDDED� ALGORITHMS�

�The� CAT28F001� integrates� the� Quick� Pulse� program-�

�ming� algorithm� on-chip,� using� the� Command� Register,�

�Status� Register� and� Write� State� Machine� (WSM).� On-�

�chip� integration� dramatically� simplifies� system� software�

�and� provides� processor-like� interface� timings� to� the�

�Command� and� Status� Registers.� WSM� operation,� inter-�

�nal� program� verify,� and� V� PP� high� voltage� presence� are�

�monitored� and� reported� via� appropriate� Status� Register�

�bits.� Figure� 4� shows� a� system� software� flowchart� for�

�device� programming.�

�As� above,� the� Quick� Erase� algorithm� is� now� imple-�

�mented� internally,� including� all� preconditioning� of� block�

�data.� WSM� operation,� erase� verify� and� V� PP� high� voltage�

�presence� are� monitored� and� reported� through� the� Status�

�Register.� Additionally,� if� a� command� other� than� Erase�

�Confirm� is� written� to� the� device� after� Erase� Setup� has�

�been� written,� both� the� Erase� Status� and� Program� Status�

�NOTES:�

�The� Write� State� Machine� Status� Bit� must� first� be� checked� to�

�determine� program� or� erase� completion,� before� the�

�Program� or� Erase� Status� bits� are� checked� for� success.�

�If� the� Program� AND� Erase� Status� bits� are� set� to� “1s”� during� an�

�erase� attempt,� an� improper� command� sequence� was�

�entered.� Attempt� the� operation� again.�

�If� V� PP� low� status� is� detected,� the� Status� Register� must� be�

�cleared� before� another� program� or� erase� operation� is�

�attempted.�

�The� V� PP� Status� bit,� unlike� an� A/D� converter,� does� not� provide�

�continuous� indication� of� V� PP� level.� The� WSM� interrogates�

�the� V� PP� level� only� after� the� program� or� erase� command�

�sequences� have� been� entered� and� informs� the� system� if�

�V� PP� has� not� been� switched� on.� The� V� PP� Status� bit� is� not�

�guaranteed� to� report� accurate� feedback� between� V� PPL� and�

�V� PPH� .�

�bits� will� be� set� to� “1”.� When� issuing� the� Erase� Setup� and�

�Erase� Confirm� commands,� they� should� be� written� to� an�

�address� within� the� address� range� of� the� block� to� be�

�erased.� Figure� 5� shows� a� system� software� flowchart� for�

�block� erase.�

�The� entire� sequence� is� performed� with� V� PP� at� V� PPH� .�

�Abort� occurs� when� RP� transitions� to� V� IL� ,� or� V� PP� drops� to�

�V� PPL� .� Although� the� WSM� is� halted,� byte� data� is� partially�

�programmed� or� Block� data� is� partially� erased� at� the�

�location� where� it� was� aborted.� Block� erasure� or� a� repeat�

�of� byte� programming� will� initialize� this� data� to� a� known�

�value.�

�BOOT� BLOCK� PROGRAM� AND� ERASE�

�The� boot� block� is� intended� to� contain� secure� code� which�

�will� minimally� bring� up� a� system� and� control� program-�

�ming� and� erase� of� other� blocks� of� the� device,� if� needed.�

�Therefore,� additional� “lockout”� protection� is� provided� to�

�guarantee� data� integrity.� Boot� block� program� and� erase�

�operations� are� enabled� through� high� voltage� V� HH� on�

�either� RP� or� OE� ,� and� the� normal� program� and� erase�

�command� sequences� are� used.� Reference� the� AC�

�Waveforms� for� Program/Erase.�

�If� boot� block� program� or� erase� is� attempted� while� RP� is�

�at� V� IH� ,� either� the� Program� Status� or� Erase� Status� bit� will�

�be� set� to� “1”,� reflective� of� the� operation� being� attempted�

�and� indicating� boot� block� lock.� Program/erase� attempts�

�while� V� IH� <� RP� <� V� HH� produce� spurious� results� and�

�should� not� be� attempted.�

�Doc.� No.� MD-1078,� Rev.� K�

�10�

�?� 2008� SCILLC.� All� rights� reserved.�

�Characteristics� subject� to� change� without� notice�

�相关PDF资料 |

PDF描述 |

|---|---|

| VI-JNP-CX-S | CONVERTER MOD DC/DC 13.8V 75W |

| GRM155R61A105KE15D | CAP CER 1UF 10V 10% X5R 0402 |

| 208008-1 | CONN D-SUB PLUG STR 25POS PCB AU |

| MBRS1540T3 | DIODE SCHOTTKY 1.5A 40V SMB |

| VI-JNL-CX-S | CONVERTER MOD DC/DC 28V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT28F001G-12TT | 功能描述:闪存 1 Megabit Boot Block 闪存 Memory RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

| CAT28F001G-12-T-T | 制造商:ON Semiconductor 功能描述:Flash Parallel 5V 1Mbit 128K x 8bit 120ns 32-Pin PLCC T/R |

| CAT28F001G-90B | 功能描述:闪存 (128x8) 1M 90ns RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

| CAT28F001G-90BT | 功能描述:闪存 1 Megabit Boot Block 闪存 Memory RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

| CAT28F001G-90T | 功能描述:闪存 (128x8) 1M 90ns RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。