- 您现在的位置:买卖IC网 > PDF目录298947 > CD74HCT138MTG4 (TEXAS INSTRUMENTS INC) HCT SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, PDSO16 PDF资料下载

参数资料

| 型号: | CD74HCT138MTG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 编、解码器及复用、解复用 |

| 英文描述: | HCT SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, PDSO16 |

| 封装: | GREEN, PLASTIC, MS-012AC, SOIC-16 |

| 文件页数: | 1/19页 |

| 文件大小: | 604K |

| 代理商: | CD74HCT138MTG4 |

1

Data sheet acquired from Harris Semiconductor

SCHS147I

Features

Select One Of Eight Data Outputs

Active Low for 138, Active High for 238

l/O Port or Memory Selector

Three Enable Inputs to Simplify Cascading

Typical Propagation Delay of 13 ns at VCC = 5 V,

CL = 15 pF, TA = 25

oC

Fanout (Over Temperature Range)

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

Wide Operating Temperature Range . . . -55oC to 125oC

Balanced Propagation Delay and Transition Times

Signicant Power Reduction Compared to LSTTL

Logic ICs

HC Types

- 2 V to 6 V Operation

- High Noise Immunity: NIL = 30%, NIH = 30% of VCC

at VCC = 5 V

HCT Types

- 4.5-V to 5.5-V Operation

- Direct LSTTL Input Logic Compatibility,

VIL= 0.8 V (Max), VIH = 2 V (Min)

- CMOS Input Compatibility, Il ≤ 1A at VOL, VOH

Description

The ’HC138, ’HC238, ’HCT138, and ’HCT238 are high-speed

silicon-gate CMOS decoders well suited to memory address

decoding or data-routing applications. Both circuits feature

low power consumption usually associated with CMOS

circuitry, yet have speeds comparable to low-power Schottky

TTL logic. Both circuits have three binary select inputs (A0,

A1, and A2). If the device is enabled, these inputs determine

which one of the eight normally high outputs of the

HC/HCT138 series go low or which of the normally low

outputs of the HC/HCT238 series go high.

Two active low and one active high enables (E1, E2, and E3)

are provided to ease the cascading of decoders. The

decoder’s eight outputs can drive ten low-power Schottky

TTL equivalent loads.

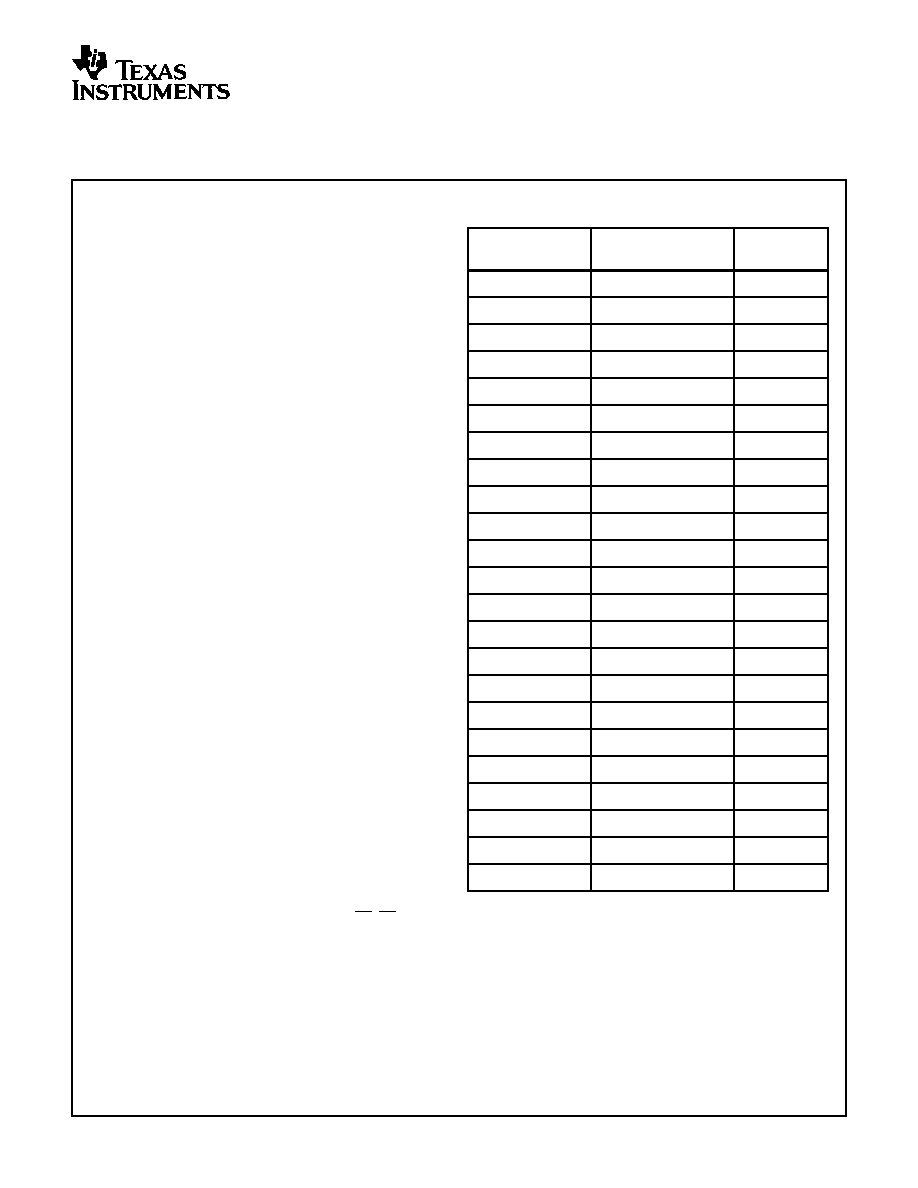

Ordering Information

PART NUMBER

TEMP. RANGE

(oC)

PACKAGE

CD54HC138F3A

-55 to 125

16 Ld CERDIP

CD54HC238F3A

-55 to 125

16 Ld CERDIP

CD54HCT138F3A

-55 to 125

16 Ld CERDIP

CD54HCT238F3A

-55 to 125

16 Ld CERDIP

CD74HC138E

-55 to 125

16 Ld PDIP

CD74HC138M

-55 to 125

16 Ld SOIC

CD74HC138MT

-55 to 125

16 Ld SOIC

CD74HC138M96

-55 to 125

16 Ld SOIC

CD74HC238E

-55 to 125

16 Ld PDIP

CD74HC238M

-55 to 125

16 Ld SOIC

CD74HC238MT

-55 to 125

16 Ld SOIC

CD74HC238M96

-55 to 125

16 Ld SOIC

CD74HC238NSR

-55 to 125

16 Ld SOP

CD74HC238PW

-55 to 125

16 Ld TSSOP

CD74HC238PWR

-55 to 125

16 Ld TSSOP

CD74HC238PWT

-55 to 125

16 Ld TSSOP

CD74HCT138E

-55 to 125

16 Ld PDIP

CD74HCT138M

-55 to 125

16 Ld SOIC

CD74HCT138MT

-55 to 125

16 Ld SOIC

CD74HCT138M96

-55 to 125

16 Ld SOIC

CD74HCT238E

-55 to 125

16 Ld PDIP

CD74HCT238M

-55 to 125

16 Ld SOIC

CD74HCT238M96

-55 to 125

16 Ld SOIC

NOTE: When ordering, use the entire part number. The sufxes 96

and R denote tape and reel. The sufx T denotes a small-quantity

reel of 250.

October 1997 - Revised August 2004

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

2004, Texas Instruments Incorporated

CD54/74HC138, CD54/74HCT138,

CD54/74HC238, CD54/74HCT238

High-Speed CMOS Logic 3- to 8-Line Decoder/

Demultiplexer Inverting and Noninverting

[ /Title

(CD74

HC138

,

CD74

HCT13

8,

CD74

HC238

,

CD74

HCT23

8)

/Sub-

ject

(High

Speed

相关PDF资料 |

PDF描述 |

|---|---|

| CD74HCT138MT | HCT SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, PDSO16 |

| CD75 | Surface Mount Power Inductors |

| CD909 | NPN PLASTIC POWER TRANSISTOR |

| CDCU877B | 1.8-V PHASE LOCK LOOP CLOCK DRIVER |

| CDEP85NP-1R4MB | 1 ELEMENT, 1.4 uH, GENERAL PURPOSE INDUCTOR, SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CD74HCT139 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CD74HCT139E | 功能描述:编码器、解码器、复用器和解复用器 Dual 2-of-4 Line RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| CD74HCT139E | 制造商:Texas Instruments 功能描述:74HCT CMOS 74HCT139 DIP16 5.5V |

| CD74HCT139EE4 | 功能描述:编码器、解码器、复用器和解复用器 High Speed CMOS Dual 2-to-4 Line RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| CD74HCT139EG4 | 功能描述:IC 2-4 LINE DECODER/DEMUX 16-DIP 制造商:texas instruments 系列:74HCT 包装:管件 零件状态:在售 类型:解码器/多路分解器 电路:1 x 2:4 独立电路:2 电流 - 输出高,低:4mA,4mA 电压源:单电源 电压 - 电源:4.5 V ~ 5.5 V 工作温度:-55°C ~ 125°C 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商器件封装:16-PDIP 基本零件编号:74HCT139 标准包装:25 |

发布紧急采购,3分钟左右您将得到回复。