- 您现在的位置:买卖IC网 > PDF目录17060 > CDB4382A (Cirrus Logic Inc)BOARD EVAL FOR CS4382A DAC PDF资料下载

参数资料

| 型号: | CDB4382A |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 14/50页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR CS4382A DAC |

| 标准包装: | 1 |

| DAC 的数量: | 8 |

| 位数: | 24 |

| 采样率(每秒): | 192k |

| 数据接口: | 串行 |

| DAC 型: | 电压 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | CS4382A |

| 产品目录页面: | 757 (CN2011-ZH PDF) |

| 相关产品: | CS4382A-DQZR-ND - IC DAC 8CH 114DB 192KHZ 48-LQFP CS4382A-DQZ-ND - IC DAC 8CH 114DB 192KHZ 48-LQFP CS4382A-CQZR-ND - IC DAC 8CH 114DB 192KHZ 48-LQFP 598-1061-ND - IC DAC 8CH 114DB 192KHZ 48LQFP |

| 其它名称: | 598-1524 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

DS618F2

21

CS4382A

4. APPLICATIONS

The CS4382A serially accepts two’s-complement formatted PCM data at standard audio sample rates including 48,

44.1, and 32 kHz in SSM, 96, 88.2, and 64 kHz in DSM, and 192, 176.4, and 128 kHz in QSM. Audio data is input

via the serial data input pins (SDINx). The Left/Right Clock (LRCK) determines which channel is currently being input

on SDINx, and the Serial Clock (SCLK) clocks audio data into the input data buffer.

The CS4382A can be configured in Hardware Mode by the M0, M1, M2, M3, and DSD_EN pins and in Software

Mode through IC or SPI.

4.1

Master Clock

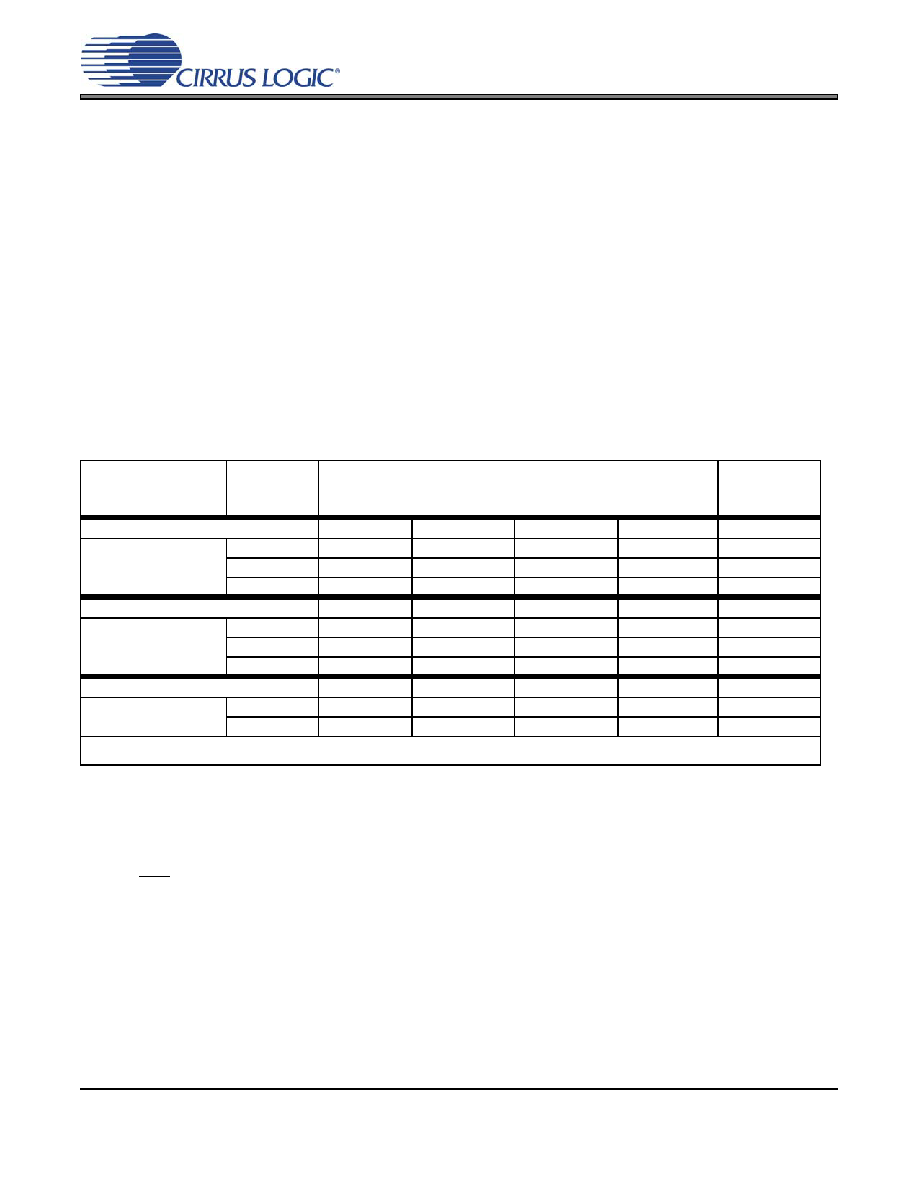

MCLK/LRCK must be an integer ratio as shown in Table 1. The LRCK frequency is equal to Fs, the frequen-

cy at which words for each channel are input to the device. The MCLK-to-LRCK frequency ratio is detected

automatically during the initialization sequence by counting the number of MCLK transitions during a single

LRCK period. Internal dividers are then set to generate the proper internal clocks. Table 1 illustrates several

standard audio sample rates and the required MCLK and LRCK frequencies. Please note there is no re-

quired phase relationship, but MCLK, LRCK, and SCLK must be synchronous.

4.2

Mode Select

In Hardware Mode, operation is determined by the Mode Select pins. The states of these pins are continu-

ally scanned for any changes; however, the mode should only be changed while the device is in reset

(RST pin low) to ensure proper switching from one mode to another. These pins require connection to sup-

ply or ground as outlined in Figure 6. VLC supplies M0, M1, and M2. VLS supplies M3 and DSD_EN.

In Software Mode, the operational mode and data format are set in the FM and DIF registers. See “Digital

Speed Mode

(sample-rate range)

Sample

Rate

(kHz)

MCLK (MHz)

Software

Mode Only

MCLK Ratio

256x

384x

512x

768x

1024x*

Single-Speed

(4 to 50 kHz)

32

8.1920

12.2880

16.3840

24.5760

32.7680

44.1

11.2896

16.9344

22.5792

33.8688

45.1584

48

12.2880

18.4320

24.5760

36.8640

49.1520

MCLK Ratio

128x

192x

256x

384x

512x*

Double-Speed

(50 to 100 kHz)

64

8.1920

12.2880

16.3840

24.5760

32.7680

88.2

11.2896

16.9344

22.5792

33.8688

45.1584

96

12.2880

18.4320

24.5760

36.8640

49.1520

MCLK Ratio

64x

96x

128x

192x

256x*

Quad-Speed

(100 to 200 kHz)

176.4

11.2896

16.9344

22.5792

33.8688

45.1584

192

12.2880

18.4320

24.5760

36.8640

49.1520

Note:

These modes are only available in Software Mode by setting the MCLKDIV bit = 1.

Table 1. Common Clock Frequencies

相关PDF资料 |

PDF描述 |

|---|---|

| 0210490183 | CABLE JUMPER 1.25MM .229M 12POS |

| VE-B3V-EY | CONVERTER MOD DC/DC 5.8V 50W |

| UPTW6181MRD | CAP ALUM 180UF 420V 20% RADIAL |

| CDB4362A | BOARD EVAL FOR CS4362A DAC |

| YLCDRSK1668S | KIT DEMONSTRATION LCD H8SX1668 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDB4383 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192 kHz 8-Channel D/A Converter |

| CDB4384 | 功能描述:音频 IC 开发工具 Eval Bd 8-Ch DAC w/DSD RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4385 | 功能描述:音频 IC 开发工具 Eval Bd 8-Ch DAC w/DSD RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4390 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit, Stereo D/A Converter for Digital Audio |

| CDB4391 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit, 192 kHz Stereo DAC with Volume Control |

发布紧急采购,3分钟左右您将得到回复。