参数资料

| 型号: | CMS82C55AZ96 |

| 厂商: | Intersil |

| 文件页数: | 26/26页 |

| 文件大小: | 0K |

| 描述: | IC I/O EXPANDER 24B 44PLCC |

| 标准包装: | 500 |

| 接口: | 可编程 |

| 输入/输出数: | 24 |

| 中断输出: | 无 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC |

| 包装: | 带卷 (TR) |

9

FN6140.2

June 15, 2006

Operating Modes

Mode 1 - (Strobed Input/Output). This functional configuration

provides a means for transferring I/O data to or from a specified

port in conjunction with strobes or “hand shaking” signals. In

mode 1, port A and port B use the lines on port C to generate or

accept these “hand shaking” signals.

Mode 1 Basic Function Definitions:

Two Groups (Group A and Group B)

Each group contains one 8-bit port and one 4-bit control/data

port

The 8-bit data port can be either input or output. Both inputs

and outputs are latched.

The 4-bit port is used for control and status of the 8-bit port.

Input Control Signal Definition

(Figures 6 and 7)

STB (Strobe Input)

A “low” on this input loads data into the input latch.

IBF (Input Buffer Full F/F)

A “high” on this output indicates that the data has been loaded

into the input latch: in essence, an acknowledgment. IBF is set

by STB input being low and is reset by the rising edge of the

RD input.

INTR (Interrupt Request)

A “high” on this output can be used to interrupt the CPU when

an input device is requesting service. INTR is set by the

condition: STB is a “one”, IBF is a “one” and INTE is a “one”. It

is reset by the falling edge of RD. This procedure allows an

input device to request service from the CPU by simply strobing

its data into the port.

INTE A

Controlled by bit set/reset of PC4.

INTE B

Controlled by bit set/reset of PC2.

Output Control Signal Definition

(Figure 8 and 9)

OBF - (Output Buffer Full F/F). The OBF output will go “low”

to indicate that the CPU has written data out to the specified

port. This does not mean valid data is sent out of the port at this

time since OBF can go true before data is available. Data is

guaranteed valid at the rising edge of OBF, (See Note 1). The

OBF F/F will be set by the rising edge of the WR input and reset

by ACK input being low.

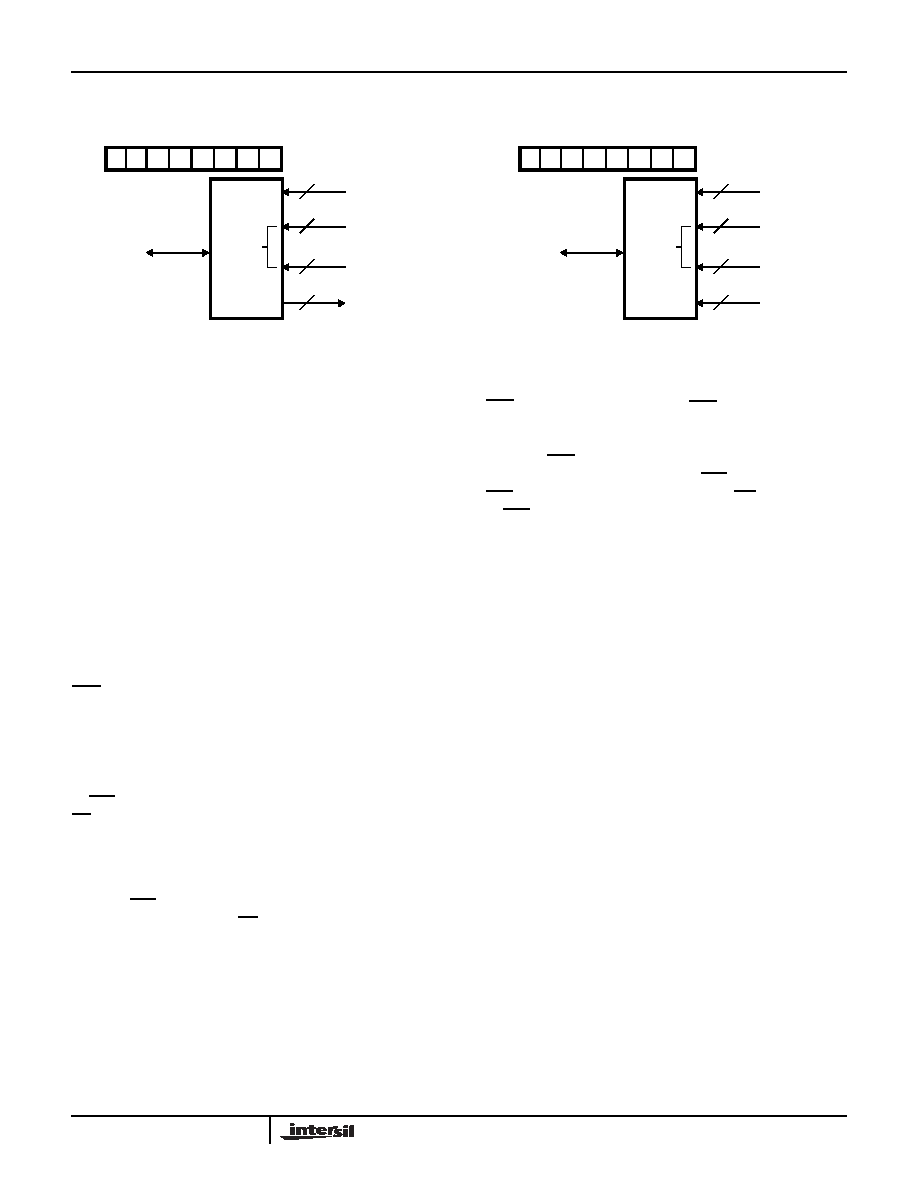

CONTROL WORD #13

CONTROL WORD #15

Mode 0 Configurations (Continued)

1

D7

0

D6

0

D5

1

D4

1

D3

0

D2

0

D1

1

D0

8

PA7 - PA0

4

PC7 - PC4

4

PC3 - PC0

8

PB7 - PB0

D7 - D0

82C55A

A

B

C

1

D7

0

D6

0

D5

1

D4

1

D3

0

D2

1

D1

1

D0

8

PA7 - PA0

4

PC7 - PC4

4

PC3 - PC0

8

PB7 - PB0

D7 - D0

82C55A

A

B

C

MS82C55A, MQ82C55A, MP82C55A

相关PDF资料 |

PDF描述 |

|---|---|

| CMS82C55AZ | IC I/O EXPANDER 24B 44PLCC |

| CS82C55A-5Z96 | IC I/O EXPANDER 24B 44PLCC |

| MCP2200-I/SO | IC USB TO UART 20SOIC |

| ATMEGA48-15MZ | MCU AVR 4K FLASH 15MHZ 32-QFN |

| CS82C55A-5Z | IC I/O EXPANDER 24B 44PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CMS8D | 制造商:SUMIDA 制造商全称:Sumida Corporation 功能描述:Strobe Light Transformer |

| CMS8D57 | 制造商:SUMIDA 制造商全称:Sumida Corporation 功能描述:Strobe Light Transformer |

| CMS8D75 | 制造商:SUMIDA 制造商全称:Sumida Corporation 功能描述:Strobe Light Transformer |

| CMS-8GB60 | 制造商:AXIOM 功能描述:Tools Development kit Interfa 制造商:AXIOM 功能描述:MC9S08GB60, RS232, SPI, DEVELOPMENT BOARD, Silicon Manufacturer:Freescale, Core 制造商:AXIOM 功能描述:MC9S08GB60, RS232, SPI, DEVELOPMENT BOARD, Silicon Manufacturer:Freescale, Core Architecture:HC08, Core Sub-Architecture:HC08, Silicon Core Number:MC9S08GB60, Silicon Family Name:68HC08, Clock Frequency:32kHz, For Use With:M9S08GB60 , RoHS Compliant: No |

| CMS-9000-G729 10P | 制造商:RadiSys 功能描述:MX S6800 G.729 CODEC LIC W/SUPT Q10 - Bulk |

发布紧急采购,3分钟左右您将得到回复。