- 您现在的位置:买卖IC网 > PDF目录379950 > COP8SGA644N9 (National Semiconductor Corporation) LMH6609 900MHz Voltage Feedback Op Amp; Package: SOIC NARROW; No of Pins: 8 PDF资料下载

参数资料

| 型号: | COP8SGA644N9 |

| 厂商: | National Semiconductor Corporation |

| 英文描述: | LMH6609 900MHz Voltage Feedback Op Amp; Package: SOIC NARROW; No of Pins: 8 |

| 中文描述: | 8位的CMOS基于ROM和OTP微控制器具有8K到32K的内存,2个比较器和USART |

| 文件页数: | 44/62页 |

| 文件大小: | 913K |

| 代理商: | COP8SGA644N9 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

12.0 MICROWIRE/PLUS

(Continued)

12.1.2 MICROWIRE/PLUS Slave Mode Operation

In the MICROWIRE/PLUS Slave mode of operation the SK

clock is generated by an external source. Setting the MSEL

bit in the CNTRL register enables the SO and SK functions

onto the G Port. The SK pin must be selected as an input

and the SO pin is selected as an output pin by setting and

resetting the appropriate bits in the Port G configuration

register. Table 11 summarizes the settings required to enter

the Slave mode of operation.

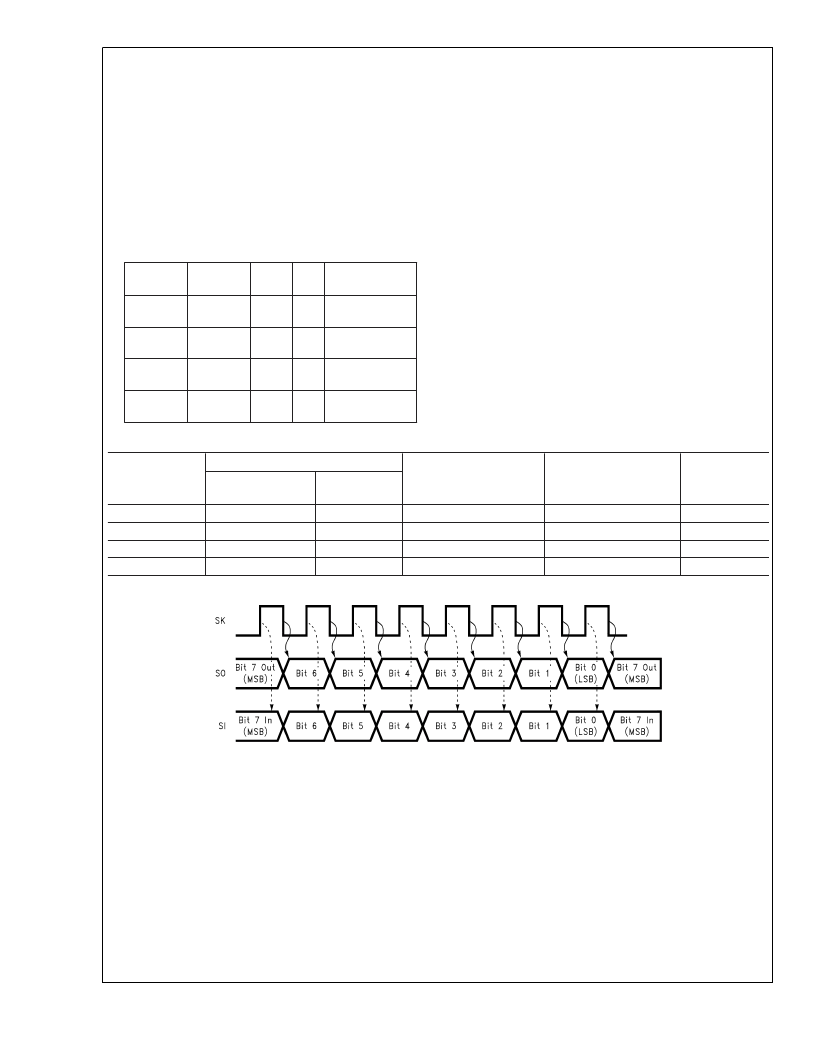

TABLE 11. MICROWIRE/PLUS Mode Settings

This table assumes that the control flag MSEL is set.

G4 (SO)

Config. Bit

1

G5 (SK)

Config. Bit

1

G4

Fun.

SO

G5

Fun.

Int.

SK

Int.

SK

Ext.

SK

Ext.

SK

Operation

MICROWIRE/PLUS

Master

MICROWIRE/PLUS

Master

MICROWIRE/PLUS

Slave

MICROWIRE/PLUS

Slave

0

1

TRI-

STATE

SO

1

0

0

0

TRI-

STATE

The user must set the BUSY flag immediately upon entering

the Slave mode. This ensures that all data bits sent by the

Master is shifted properly. After eight clock pulses the BUSY

flag is clear, the shift clock is stopped, and the sequence

may be repeated.

12.1.3 Alternate SK Phase Operation and SK Idle P

The device allows either the normal SK clock or an alternate

phase SK clock to shift data in and out of the SIO register. In

both the modes the SK idle polarity can be either high or low.

The polarity is selected by bit 5 of Port G data register. In the

normal mode data is shifted in on the rising edge of the SK

clock and the data is shifted out on the falling edge of the SK

clock. In the alternate SK phase operation, data is shifted in

on the falling edge of the SK clock and shifted out on the

rising edge of the SK clock. Bit 6 of Port G configuration

register selects the SK edge.

A control flag, SKSEL, allows either the normal SK clock or

the alternate SK clock to be selected. Resetting SKSEL

causes the MICROWIRE/PLUS logic to be clocked from the

normal SK signal. Setting the SKSEL flag selects the alter-

nate SK clock. The SKSEL is mapped into the G6 configu-

ration bit. The SKSEL flag will power up in the reset condi-

tion, selecting the normal SK signal.

TABLE 12. MICROWIRE/PLUS Shift Clock Polarity and Sample/Shift Phase

Port G

SK Phase

G6 (SKSEL)

Config. Bit

0

1

0

1

G5 Data

Bit

0

0

1

1

SO Clocked Out On:

SI Sampled On:

SK Idle

Phase

Normal

Alternate

Alternate

Normal

SK Falling Edge

SK Rising Edge

SK Rising Edge

SK Falling Edge

SK Rising Edge

SK Falling Edge

SK Falling Edge

SK Rising Edge

Low

Low

High

High

10131733

FIGURE 29. MICROWIRE/PLUS SPI Mode Interface Timing, Normal SK Mode, SK Idle Phase being Low

C

www.national.com

44

相关PDF资料 |

PDF描述 |

|---|---|

| COP8SGA644Q6 | LMH6609 900MHz Voltage Feedback Op Amp; Package: SOIC NARROW; No of Pins: 8 |

| COP8SGA644Q7 | LMH6609 900MHz Voltage Feedback Op Amp; Package: SOT-23; No of Pins: 5 |

| COP8SGA644Q8 | LMH6609 900MHz Voltage Feedback Op Amp; Package: SOT-23; No of Pins: 5 |

| COP8SGA644Q9 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA644V3 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

相关代理商/技术参数 |

参数描述 |

|---|---|

| COP8SGA644Q3 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA644Q6 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA644Q7 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA644Q8 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA644Q9 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

发布紧急采购,3分钟左右您将得到回复。