- 您现在的位置:买卖IC网 > PDF目录11567 > CP82C59A (Intersil)IC CONTROLLER CMOS 28P-DIP PDF资料下载

参数资料

| 型号: | CP82C59A |

| 厂商: | Intersil |

| 文件页数: | 6/22页 |

| 文件大小: | 0K |

| 描述: | IC CONTROLLER CMOS 28P-DIP |

| 标准包装: | 143 |

| 控制器类型: | CMOS 优先中断控制器 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 1mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 28-DIP(0.600",15.24mm) |

| 供应商设备封装: | 28-PDIP |

| 包装: | 管件 |

14

FN2784.5

March 17, 2006

The difficulty here is that if an Interrupt Request is

acknowledged and an End of Interrupt command did not

reset its IS bit (i.e., while executing a service routine), the

82C59A would have inhibited all lower priority requests with

no easy way for the routine to enable them.

That is where the Special Mask Mode comes in. In the

Special Mask Mode, when a mask bit is set in OCW1, it

inhibits further interrupts at that level and enables interrupts

from all other levels (lower as well as higher) that are not

masked.

Thus, any interrupts may be selectively enabled by loading

the mask register.

The Special Mask Mode is set by OCW3 where: ESMM = 1,

SMM = 1, and cleared where ESMM = 1, SMM = 0.

Poll Command

In this mode, the INT output is not used or the

microprocessor internal Interrupt Enable flip flop is reset,

disabling its interrupt input. Service to devices is achieved by

software using a Poll command.

The Poll command is issued by setting P = 1 in OCW3. The

82C59A treats the next RD pulse to the 82C59A (i.e., RD =

0, CS = 0) as an interrupt acknowledge, sets the appropriate

IS bit if there is a request, and reads the priority level.

Interrupt is frozen from WR to RD.

The word enabled onto the data bus during RD is:

W0 - W2: Binary code of the highest priority level request-

ing service.

I:

Equal to a “1” if there is an interrupt.

This mode is useful if there is a routine command common to

several levels so that the INTA sequence is not needed

(saves ROM space). Another application is to use the poll

mode to expand the number of priority levels to more than 64.

D7

D6

D5

D4

D3

D2

D1

D0

I

----

W2

W1

W0

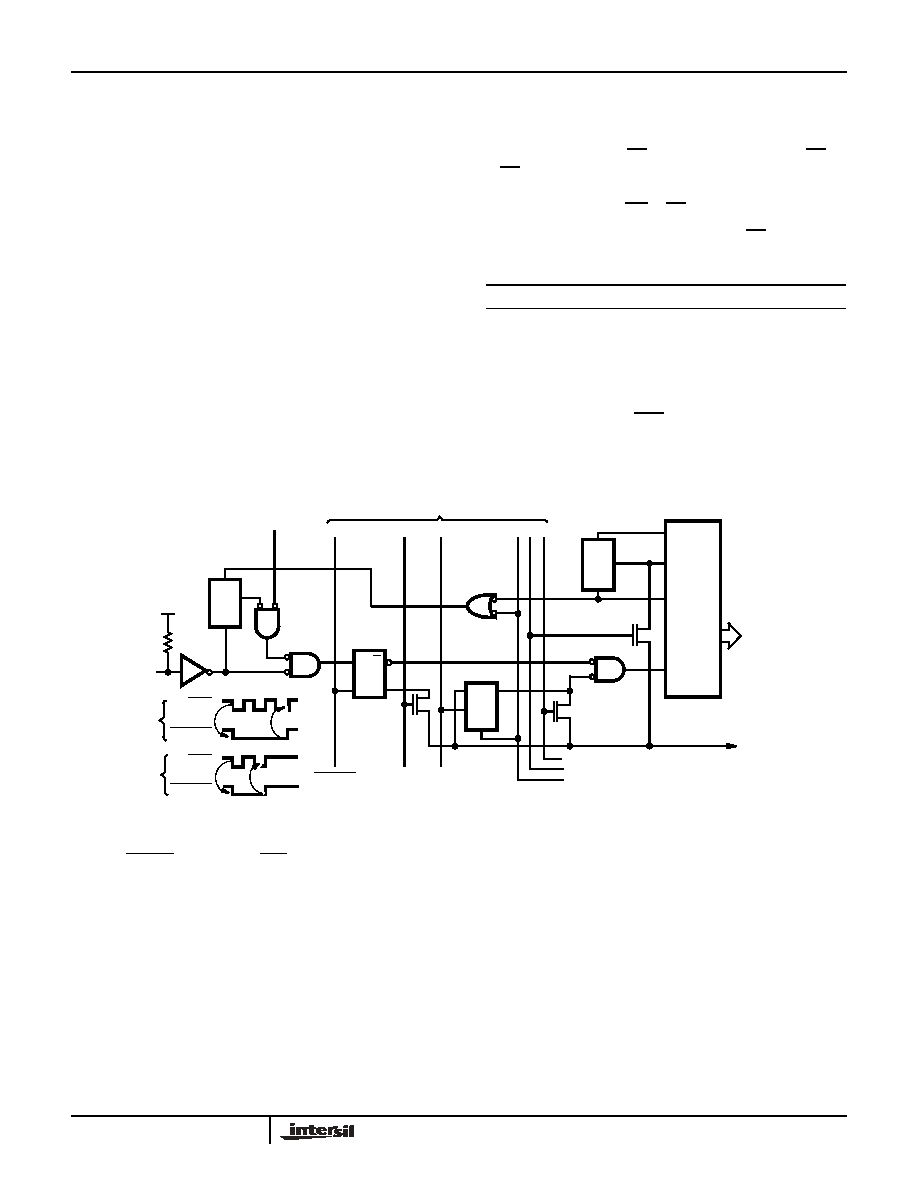

EDGE

SENSE

LATCH

LTIM BIT

0 = EDGE

1 = LEVEL

VCC

IR

8080/85

MODE

80C86/

88/286

MODE

INTA

FREEZE

INTA

FREEZE

READ

IRR

WRITE

MASK

READ IMR

READ ISR

MASTER CLEAR

MASK LATCH

REQUEST

LATCH

IN - SERVICE

LATCH

NON-

MASKED

REQ

CLR

Q

SET

TO OTHER PRIORITY CELLS

PRIORITY

RESOLVER

CONTROL

LOGIC

SET ISR

CLR ISR

ISR BIT

Q

D

C

CLR

Q

D

CQ

CLR

SET

Q

NOTES:

1. Master clear active only during ICW1.

2. FREEZE is active during INTA and poll sequence only.

3. Truth Table for D-latch.

C

D

Q

Operation

1D1

D1

Follow

0X

Qn-1

Hold

82C59A

相关PDF资料 |

PDF描述 |

|---|---|

| PIC16F627AT-E/SO | IC MCU FLASH 1KX14 EEPROM 18SOIC |

| PIC16LF720-I/P | MCU PIC 2K FLASH 20-DIP |

| PIC24F16KL401T-I/SS | IC MCU 16BIT 16KB FLASH 20-SSOP |

| PIC24F08KL402T-I/SO | IC MCU 16BIT 8KB FLASH 28-SOIC |

| PIC16LF1783-E/SO | IC MCU 8BIT 7KB FLASH 28-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CP82C59A-12 | 功能描述:IC INTERFACE 5V 12.5MHZ 28-DIP RoHS:否 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| CP82C59A-12Z | 功能描述:接口 - 专用 W/ANNEAL PERIPH INT CNTRLR 5V 12 5MHZ RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| CP82C59A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CP82C59AS2065 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CP82C59AS2485 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。