- 您现在的位置:买卖IC网 > PDF目录10216 > CS181012-CQZ (Cirrus Logic Inc)IC COBRANET CS181012 144LQFP PDF资料下载

参数资料

| 型号: | CS181012-CQZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 5/15页 |

| 文件大小: | 0K |

| 描述: | IC COBRANET CS181012 144LQFP |

| 标准包装: | 60 |

| 系列: | CobraNet® |

| 类型: | 音频处理器 |

| 应用: | 网络 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

| 产品目录页面: | 758 (CN2011-ZH PDF) |

| 配用: | 598-1021-ND - MODULE COBRANET 4961 CM2 FB 598-1020-ND - MODULE COBRANET 1810 CM2 MT |

| 其它名称: | 598-1025 |

CobraNet Hardware User’s Manual

Pinout and Signal Descriptions

DS651UM23

Copyright 2005 Cirrus Logic, Inc.

13

Version 2.3

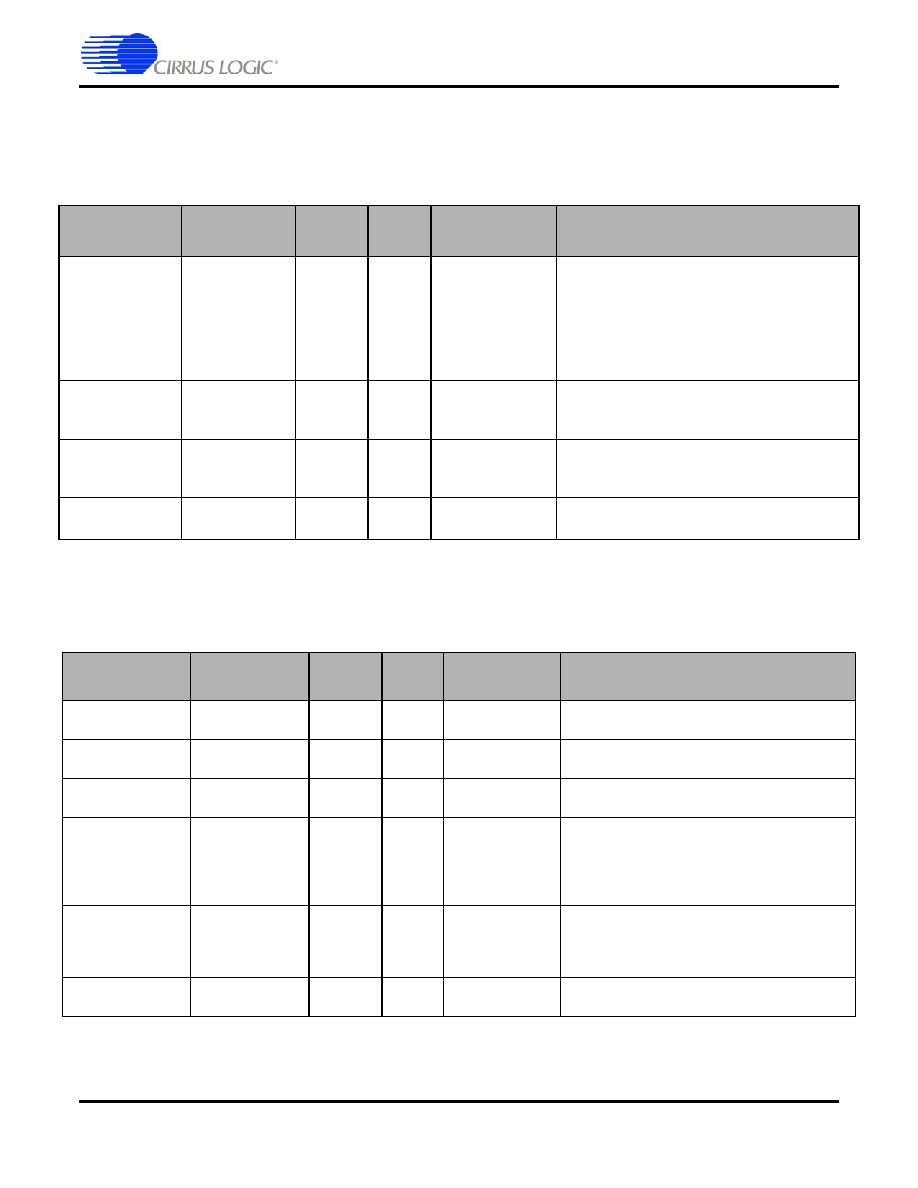

4.2.3 Synchronous Serial (Audio) Signals

The synchronous serial interfaces are used to bring digital audio into and out of the

system. Typically the synchronous serial is wired to ADCs and/or DACs. Detailed timing

and format is described in "Digital Audio Interface" on page 19.

4.2.4 Audio Clock Signals

See "Synchronization" on page 17 for an overview of synchronization modes and issues.

*An external multiplexor controlled by this pin is required for full MCLK_IN and MCLK out

implementation.

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

DAO1_SCLK

Audio Bit Clock

Out

J3:A7

20

Synchronous serial bit clock.

64 FS for CS18100x & CS49610x (2x1 channel)

64 FS for CS18101x & CS49611x (2x4

channels)

128 FS for CS18102x & CS49612x (4x4

channels)

Typically tied to DAI1_SCLK.

DAO1_DATA[3:0]

Audio Output

Data

Out

J3:A18,

B18

15-17, 19

Output synchronous serial audio data

DAO1_DATA[3:1] not used for CS18100x &

CS49610x.

DAI1_DATA[3:0]

Audio Input Data

In

J3:

A[15:12]

131, 132, 134, 135

Input synchronous serial audio data

DAI1_DATA[3:1] not used for CS18100x &

CS49610x.

DAI1_SCLK

Audio Bit Clock

In

J4:A7

137

Should be tied to DAO1_SCLK.

Synchronous serial bit clock.

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

DAI1_LRCLK

Sample clock

input

In

138

Should be tied to DAO1_LRCLK for all devices.

DAO1_LRCLK

(FS1)

Sample clock

output

Out

J3:A3

22

FS1 (word clock) for CS18100x/CS49610x and

CS18101x/CS49611x.

DAO2_LRCLK

(FS1)

Sample clock

output

Out

J3:A3

14

FS1 (word clock) for CS18102x & CS49612x.

REFCLK_IN

Reference clock

In

J3:A6

97

Clock input for synchronizing network to an

external clock source, for redundancy control

and synchronization of FS divider chain to

external source. See "Synchronization" on

page 17 for more detail.

MCLK_IN

Master audio

clock input

In

J3:A5

8*

For systems featuring multiple CobraNet

interfaces operating off a common master

clock. See "Synchronization" on page 17 for

more detail.

MCLK_OUT

Master audio

clock output

Out

J3:A4

8*

Low jitter 24.576 MHz master audio clock.

相关PDF资料 |

PDF描述 |

|---|---|

| T 3504 018 | CONN MALE 8POS CABLE MNT GOLD |

| CXS3106A14S1S | CONN PLUG 3POS STRGHT SKT |

| SP3483CN-L/TR | IC TXRX RS485 HALF DUPLEX 8NSOIC |

| D7MB | CONN RCPT MALE 7PIN BLACK/SILVER |

| SP3223EUCY-L/TR | IC TXRX RS232 INTELLIGNT 20TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS181012-CQZ/A1 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Digital Audio Networking Processor |

| CS181012-CQZA1 | 制造商:Cirrus Logic 功能描述: |

| CS181012-CQZR | 功能描述:音频 DSP IC CobraNet Audio Networking Processor RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| CS181022-CM2-FB | 制造商:Cirrus Logic 功能描述: |

| CS181022-CQ | 功能描述:音频 DSP IC CobraNet Audio Networking Processor RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。