- 您现在的位置:买卖IC网 > PDF目录10217 > CS181022-CQZR (Cirrus Logic Inc)IC COBRANET 16CH 32BIT 144-LQFP PDF资料下载

参数资料

| 型号: | CS181022-CQZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 5/15页 |

| 文件大小: | 0K |

| 描述: | IC COBRANET 16CH 32BIT 144-LQFP |

| 标准包装: | 500 |

| 系列: | CobraNet® |

| 类型: | 音频处理器 |

| 应用: | 网络 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 带卷 (TR) |

| 配用: | 598-1021-ND - MODULE COBRANET 4961 CM2 FB 598-1020-ND - MODULE COBRANET 1810 CM2 MT |

CobraNet Hardware User’s Manual

Pinout and Signal Descriptions

DS651UM23

Copyright 2005 Cirrus Logic, Inc.

13

Version 2.3

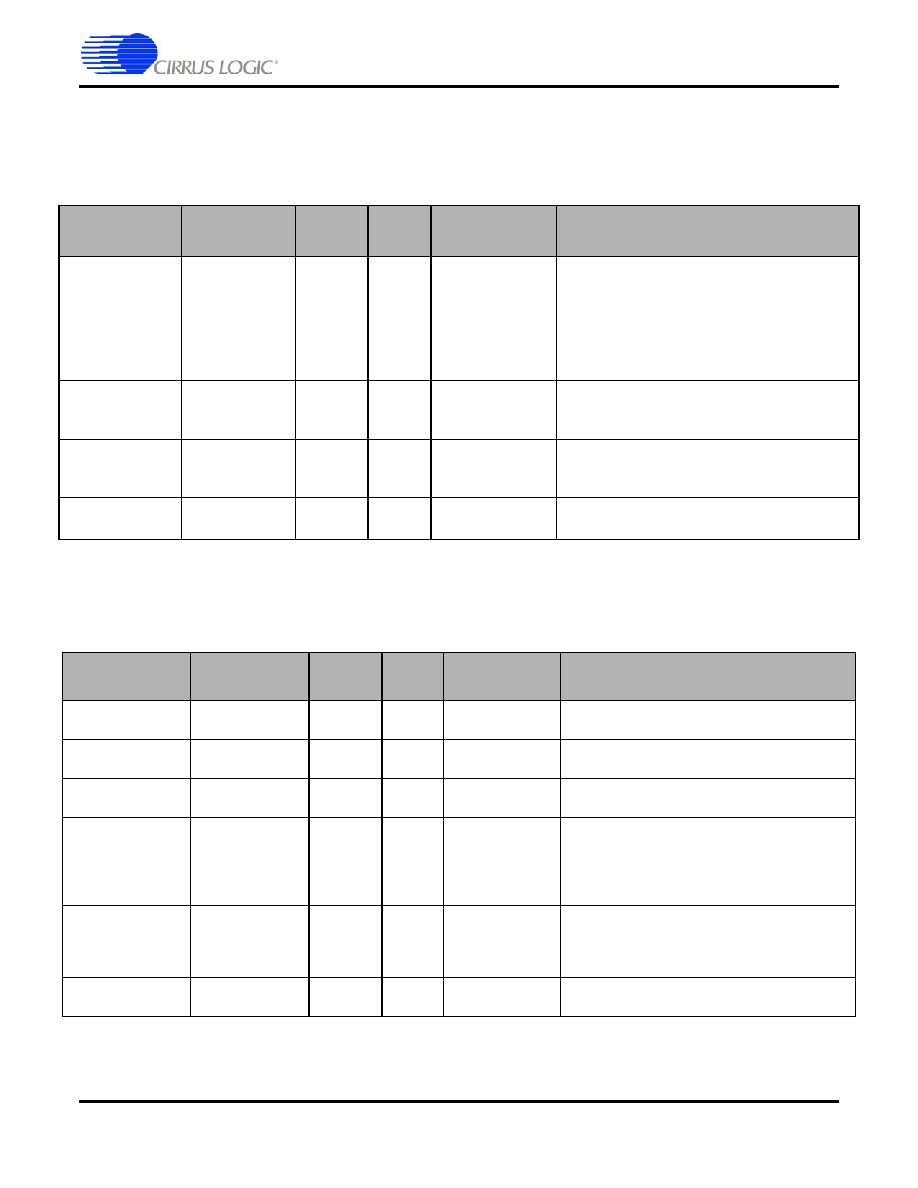

4.2.3 Synchronous Serial (Audio) Signals

The synchronous serial interfaces are used to bring digital audio into and out of the

system. Typically the synchronous serial is wired to ADCs and/or DACs. Detailed timing

and format is described in "Digital Audio Interface" on page 19.

4.2.4 Audio Clock Signals

See "Synchronization" on page 17 for an overview of synchronization modes and issues.

*An external multiplexor controlled by this pin is required for full MCLK_IN and MCLK out

implementation.

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

DAO1_SCLK

Audio Bit Clock

Out

J3:A7

20

Synchronous serial bit clock.

64 FS for CS18100x & CS49610x (2x1 channel)

64 FS for CS18101x & CS49611x (2x4

channels)

128 FS for CS18102x & CS49612x (4x4

channels)

Typically tied to DAI1_SCLK.

DAO1_DATA[3:0]

Audio Output

Data

Out

J3:A18,

B18

15-17, 19

Output synchronous serial audio data

DAO1_DATA[3:1] not used for CS18100x &

CS49610x.

DAI1_DATA[3:0]

Audio Input Data

In

J3:

A[15:12]

131, 132, 134, 135

Input synchronous serial audio data

DAI1_DATA[3:1] not used for CS18100x &

CS49610x.

DAI1_SCLK

Audio Bit Clock

In

J4:A7

137

Should be tied to DAO1_SCLK.

Synchronous serial bit clock.

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

DAI1_LRCLK

Sample clock

input

In

138

Should be tied to DAO1_LRCLK for all devices.

DAO1_LRCLK

(FS1)

Sample clock

output

Out

J3:A3

22

FS1 (word clock) for CS18100x/CS49610x and

CS18101x/CS49611x.

DAO2_LRCLK

(FS1)

Sample clock

output

Out

J3:A3

14

FS1 (word clock) for CS18102x & CS49612x.

REFCLK_IN

Reference clock

In

J3:A6

97

Clock input for synchronizing network to an

external clock source, for redundancy control

and synchronization of FS divider chain to

external source. See "Synchronization" on

page 17 for more detail.

MCLK_IN

Master audio

clock input

In

J3:A5

8*

For systems featuring multiple CobraNet

interfaces operating off a common master

clock. See "Synchronization" on page 17 for

more detail.

MCLK_OUT

Master audio

clock output

Out

J3:A4

8*

Low jitter 24.576 MHz master audio clock.

相关PDF资料 |

PDF描述 |

|---|---|

| MS3102A8S-1S | CONN RCPT 1POS BOX MNT W/SCKT |

| MS27497T20B41PB | CONN RCPT 41POS WALL MNT W/PINS |

| CS8427-CSZ | IC TXRX DGTL AUDIO 96KHZ 28SOIC |

| AD7893ARZ-2REEL | IC ADC 12BIT SRL T/H LP 8SOIC |

| MS27467T11B4PC | CONN PLUG 4POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS1810XX | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:New CobraNet Silicon Series Ideal for Digital Audio Networking Applications |

| CS1812-04 | 制造商:CITRUSCOM 功能描述:EMI with ESD protection IC uDFN-8L |

| CS1812-08 | 制造商:CITRUSCOM 功能描述: |

| CS18124 | 功能描述:电气外壳 SCREW COVER NO KO’S 18 x 12 x 4" RoHS:否 制造商:Bud Industries 产品:Wall Mount Enclosures 类型:Single Door NEMA 额定值:3R 外部深度:254 mm 外部高度:305 mm 外部宽度:305 mm 面板宽度:261 mm 面板高度:261 mm 材料:Steel 颜色:Gray 通风:Not Available |

| CS18126 | 功能描述:电气外壳 SCREW COVER NO KO’S 18 x 12 x 6" RoHS:否 制造商:Bud Industries 产品:Wall Mount Enclosures 类型:Single Door NEMA 额定值:3R 外部深度:254 mm 外部高度:305 mm 外部宽度:305 mm 面板宽度:261 mm 面板高度:261 mm 材料:Steel 颜色:Gray 通风:Not Available |

发布紧急采购,3分钟左右您将得到回复。