- 您现在的位置:买卖IC网 > PDF目录380066 > CS4202 (Cirrus Logic, Inc.) IC EEPROM SRL 128X8BIT 8DIP PDF资料下载

参数资料

| 型号: | CS4202 |

| 厂商: | Cirrus Logic, Inc. |

| 英文描述: | IC EEPROM SRL 128X8BIT 8DIP |

| 中文描述: | 音频编解码器97耳机放大器 |

| 文件页数: | 18/68页 |

| 文件大小: | 1248K |

| 代理商: | CS4202 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

CS4202

18

DS549PP1

3.2

AC-Link Serial Data Input Frame

In the serial data input frame, data is passed on the SDATA_IN pin from the CS4202 to the AC ’97 con-

troller. The data format for the input frame is very similar to the output frame. Figure 9 on page 15 illus-

trates the serial port timing.

The PCMcapturedatafrom theCS4202 is shifted out MSB first in themost significant 18 bits ofeach slot.

The least significant 2 bits in each slot will be ‘cleared’. If the host requests PCM data from the AC ’97

Controller that is less than 18 bits wide, the controller should dither and round or just round (but not trun-

cate) to the desired bit depth.

Bits that are reserved or not implemented in the CS4202 will always be returned ‘cleared’.

3.2.1

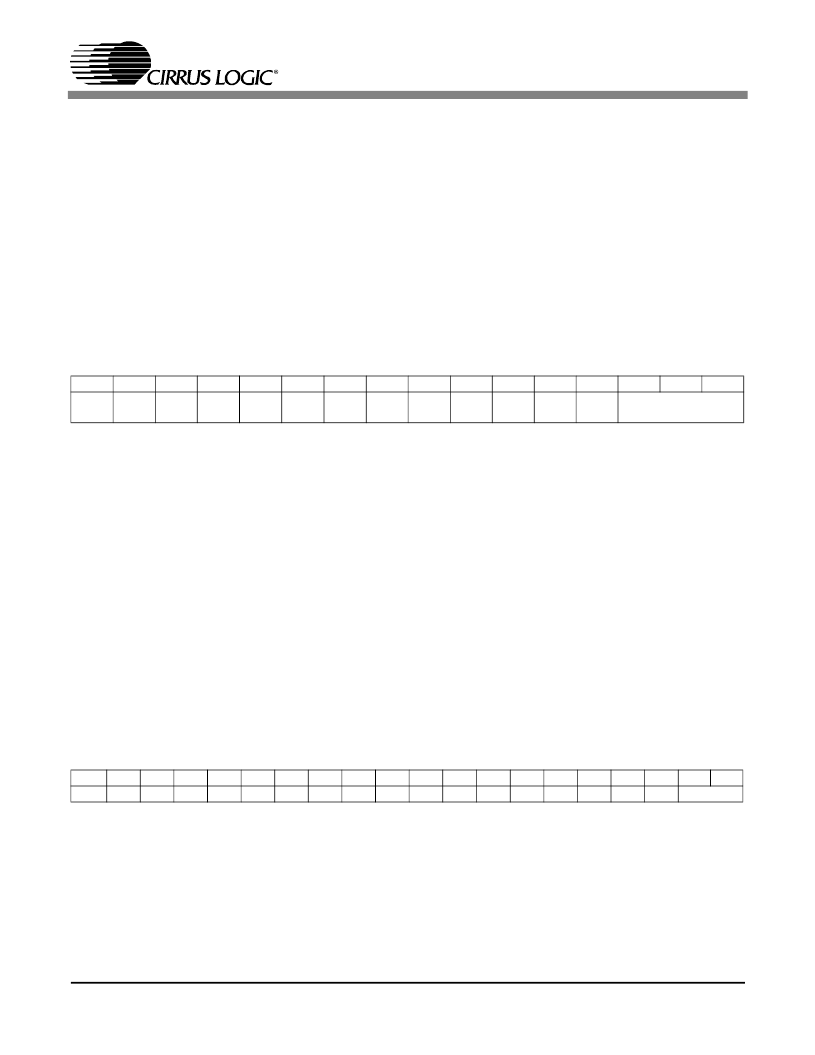

Serial Data Input Slot Tag Bits (Slot 0)

Codec Ready

Codec Ready. The Codec Ready bit indicates the readiness of the CS4202 AC-link. Immedi-

ately after a Cold Reset this bit will be ‘clear’. Once the CS4202 clocks and voltages are sta-

ble, this bit will be ‘set’. Until the Codec Ready bit is ‘set’, no AC-link transactions should be

attempted by the controller. The Codec Ready bit does not indicate readiness of the DACs,

ADCs, Vref, or any other analog function. Those must be checked in the

Powerdown Con-

trol/Status Register (Index 26h)

by the controller before any access is made to the mixer reg-

isters. Any accesses to the CS4202 while Codec Ready is ‘clear’ are ignored.

Slot 1 Valid

The Slot 1 Valid bit indicates Slot 1 contains a valid read back address.

Slot 2 Valid

The Slot 2 Valid bit indicates Slot 2 contains valid register read data.

Slot [3:4,6:8,11] Valid The Slot [3:4,6:8,11] Valid bits indicate Slot [3:4,6:8,11] contains valid capture data from the

CS4202 ADCs. If a bit is ‘set’, the corresponding input slot contains valid data. If a bit is

‘cleared’, the corresponding slot will be ignored.

Slot 12 Valid

The Slot 12 Valid bit indicates Slot 12 contains valid GPIO status data.

3.2.2

Status Address Port (Slot 1)

RI[6:0]

Register Index. The RI[6:0] bits echo the AC ’97 register address when a register read has

been requested in the previous frame. The CS4202 will only echo the register index for a read

access. Write accesses will not return valid data in Slot 1.

SR[3:4,6:11]

Slot Request. If SRx is ‘set’, this indicates the CS4202 SRC does not need a new sample on

the nextAC-link frame for that particular slot. If SRx is ‘clear’,the SRC indicates a new sample

is needed on the following frame. Ifthe VRA bit in the

Extended Audio Status/Control Register

(Index 2Ah)

is ‘clear’, the SR[3:4,6:11] bits are always 0. When VRA is ‘set’, the SRC is en-

abled and the SR[3:4,6:11] bits are used to request data.

Bit 15

Codec

Ready

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Slot 1

Valid

Slot 2

Valid

Slot 3

Valid

Slot 4

Valid

0

Slot 6

Valid

Slot 7

Valid

Slot 8

Valid

0

0

Slot 11

Valid

Slot12

Valid

Reserved

Bit 19

Res

18

RI6

17

RI5

16

RI4

15

RI3

14

RI2

13

RI1

12

RI0

11

SR3 SR4

10

9

0

8

7

6

5

4

3

2

0

1

0

SR6 SR7 SR8 SR9 SR10 SR11

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| CS4205 | CrystalClear Audio Codec 97 with Portable Computing |

| CS4205-KQ | CrystalClear Audio Codec 97 with Portable Computing |

| CS4210 | IEEE 1394 OHCI Controller |

| CS4210VJG | IEEE 1394 OHCI Controller |

| CS4215-KL | 16-Bit Multimedia Audio Codec |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS420-2 | 制造商:Captive Fastener Corporation 功能描述: |

| CS4202_05 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Audio Codec ’97 with Headphone Amplifier |

| CS4202-JQ | 功能描述:接口—CODEC IC AC’97 CODEC w/Headphone Amp RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4202-JQZ | 功能描述:接口—CODEC IC AC’97 w/Headphone Amp RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4202-JQZ | 制造商:Cirrus Logic 功能描述:Audio CODEC IC |

发布紧急采购,3分钟左右您将得到回复。